## Complete DDR2/3 memory power supply controller

### Features

- Switching section (VDDQ)

- 4.5 V to 28 V input voltage range

- 0.9 V,  $\pm 1\%$  voltage reference

- 1.8 V (DDR2) or 1.5 V (DDR3) fixed output voltages

- 0.9 V to 2.6 V adjustable output voltage

- 1.237 V  $\pm 1\%$  reference voltage available

- Very fast load transient response using constant on-time control loop

- No  $R_{SENSE}$  current sensing using low side MOSFET's  $R_{DS(ON)}$

- Negative current limit

- Latched OVP and UVP

- Soft-start internally fixed at 3 ms

- Selectable pulse skipping at light load

- Selectable no-audible (33 kHz) pulse skip mode

- Ceramic output capacitors supported

- Output voltage ripple compensation

- VTT LDO and VTTREF

- 2 Apk LDO with foldback for VTT

- Remote VTT sensing

- High-Z VTT output in S3

- Ceramic output capacitors supported

- $\pm 15$  mA low noise buffered reference

### Applications

- DDR2/3 memory supply

- Notebook computers

- Handheld and PDAs

- CPU and chipset I/O supplies

- SSTL18, SSTL15 and HSTL bus termination

### Description

The device PM6670S is a complete DDR2/3 power supply regulator designed to meet JEDEC specifications.

It integrates a constant on-time (COT) buck controller, a 2 Apk sink/source low drop out regulator and a 15 mA low noise buffered reference.

The COT architecture assures fast transient response supporting both electrolytic and ceramic output capacitors. An embedded integrator control loop compensates the DC voltage error due to the output ripple.

The 2 Apk sink/source linear regulator provides the memory termination voltage with fast load transient response.

The device is fully compliant with system sleep states S3 and S4/S5, providing LDO output high impedance in suspend-to-RAM and tracking discharge of all outputs in suspend-to-disk.

**Table 1. Device summary**

| Order code | Package       | Packaging     |

|------------|---------------|---------------|

| PM6670S    | VFQFPN-24 4x4 | Tube          |

| PM6670STR  | (Exposed pad) | Tape and reel |

## Contents

|          |                                                |           |

|----------|------------------------------------------------|-----------|

| <b>1</b> | <b>Typical application circuit</b>             | <b>4</b>  |

| <b>2</b> | <b>Pin settings</b>                            | <b>5</b>  |

| 2.1      | Connections                                    | 5         |

| 2.2      | Pin description                                | 6         |

| <b>3</b> | <b>Electrical data</b>                         | <b>8</b>  |

| 3.1      | Maximum rating                                 | 8         |

| 3.2      | Thermal data                                   | 8         |

| 3.3      | Recommended operating conditions               | 9         |

| <b>4</b> | <b>Electrical characteristics</b>              | <b>10</b> |

| <b>5</b> | <b>Typical operating characteristics</b>       | <b>14</b> |

| <b>6</b> | <b>Block diagram</b>                           | <b>19</b> |

| <b>7</b> | <b>Device description</b>                      | <b>20</b> |

| 7.1      | VDDQ section - constant on-time PWM controller | 21        |

| 7.1.1    | Constant-on-time architecture                  | 23        |

| 7.1.2    | Output ripple compensation and loop stability  | 24        |

| 7.1.3    | Pulse-skip and no-audible pulse-skip modes     | 28        |

| 7.1.4    | Mode-of-operation selection                    | 30        |

| 7.1.5    | Current sensing and current limit              | 31        |

| 7.1.6    | POR, UVLO and soft-start                       | 32        |

| 7.1.7    | Power Good signal                              | 33        |

| 7.1.8    | VDDQ output discharge                          | 34        |

| 7.1.9    | Gate drivers                                   | 35        |

| 7.1.10   | Reference voltage and bandgap                  | 35        |

| 7.1.11   | Over voltage and under voltage protections     | 36        |

| 7.1.12   | Device thermal protection                      | 36        |

| 7.2      | VTTREF buffered reference and VTT LDO section  | 37        |

| 7.2.1    | VTT and VTTREF Soft-Start                      | 37        |

| 7.2.2    | VTTREF and VTT outputs discharge               | 37        |

|           |                                    |           |

|-----------|------------------------------------|-----------|

| 7.3       | S3 and S5 power management pins    | 38        |

| <b>8</b>  | <b>Application information</b>     | <b>39</b> |

| 8.1       | External components selection      | 39        |

| 8.1.1     | Inductor selection                 | 41        |

| 8.1.2     | Input capacitor selection          | 42        |

| 8.1.3     | Output capacitor selection         | 43        |

| 8.1.4     | MOSFETs selection                  | 44        |

| 8.1.5     | Diode selection                    | 46        |

| 8.1.6     | VDDQ current limit setting         | 47        |

| 8.1.7     | All ceramic capacitors application | 48        |

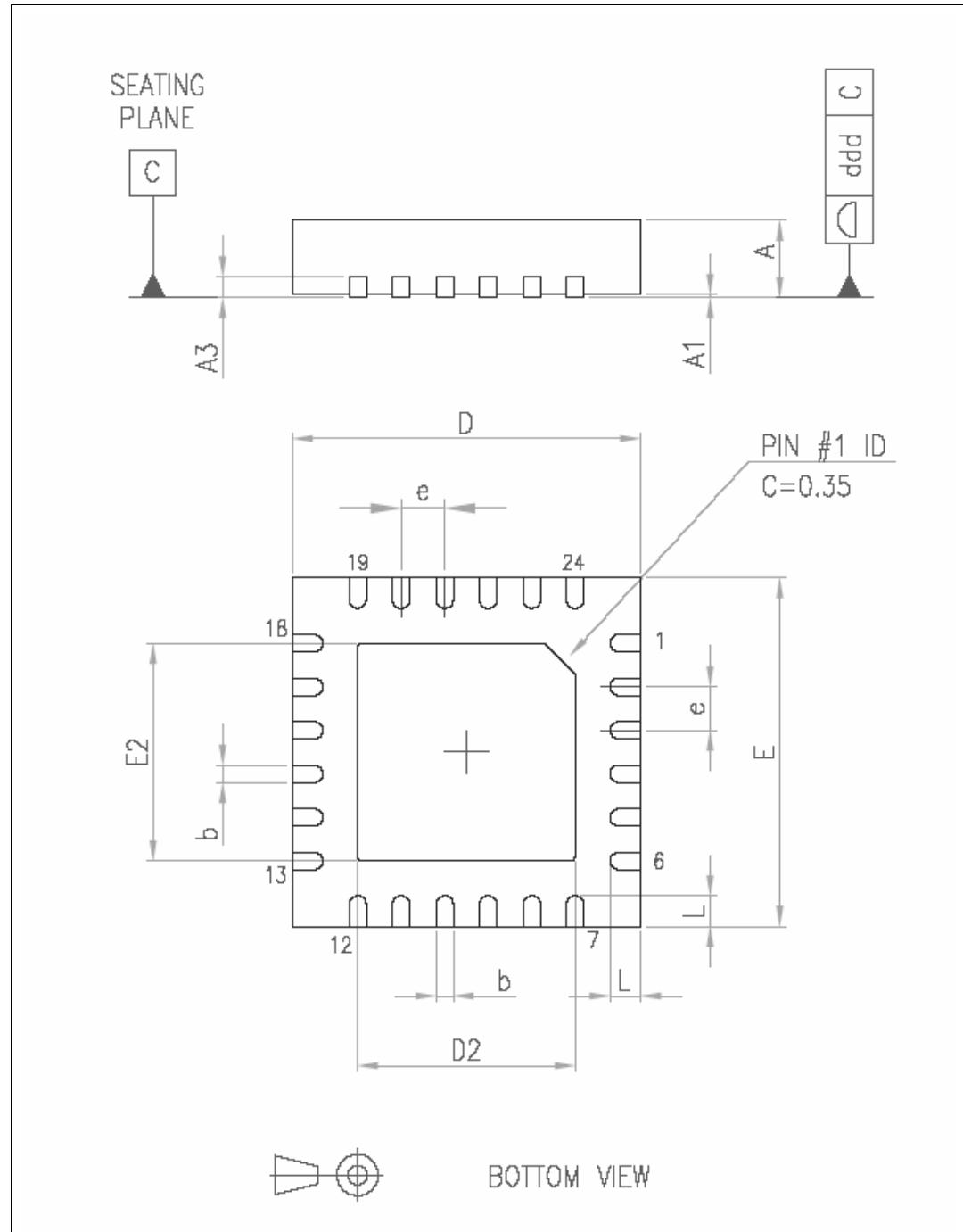

| <b>9</b>  | <b>Package mechanical data</b>     | <b>51</b> |

| <b>10</b> | <b>Revision history</b>            | <b>53</b> |

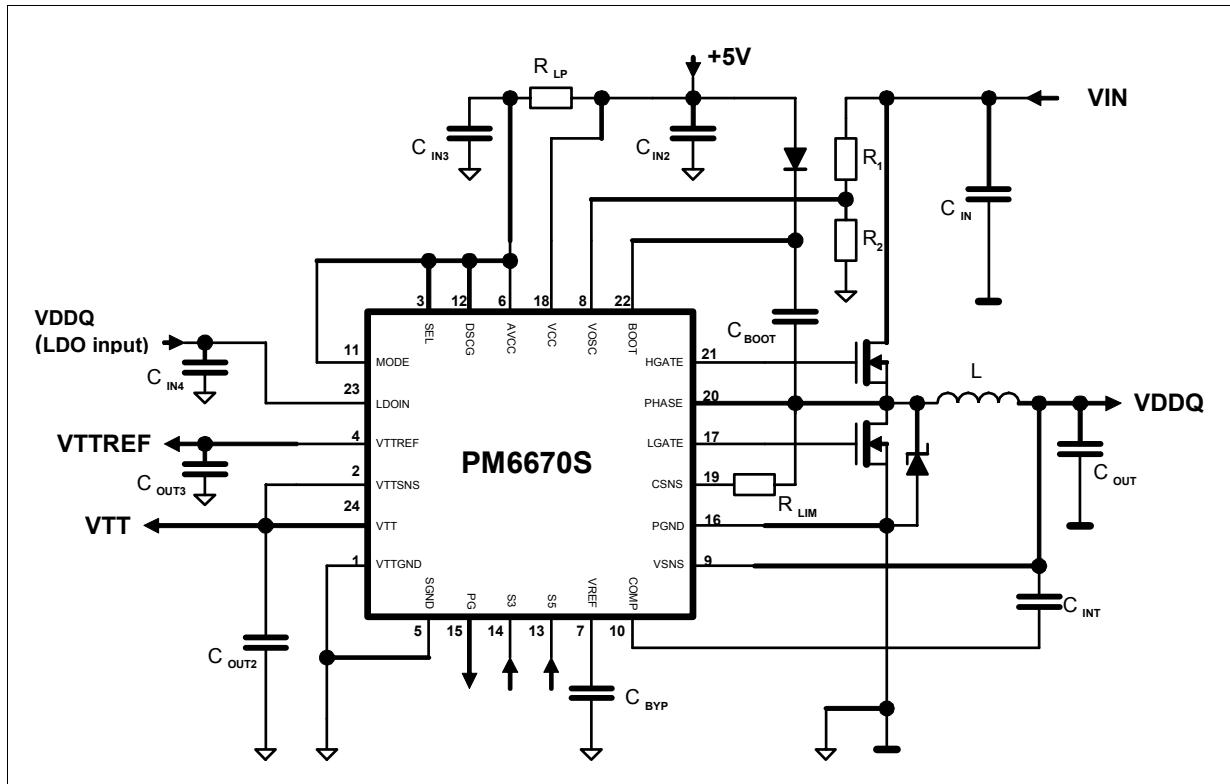

## 1 Typical application circuit

**Figure 1. Application circuit**

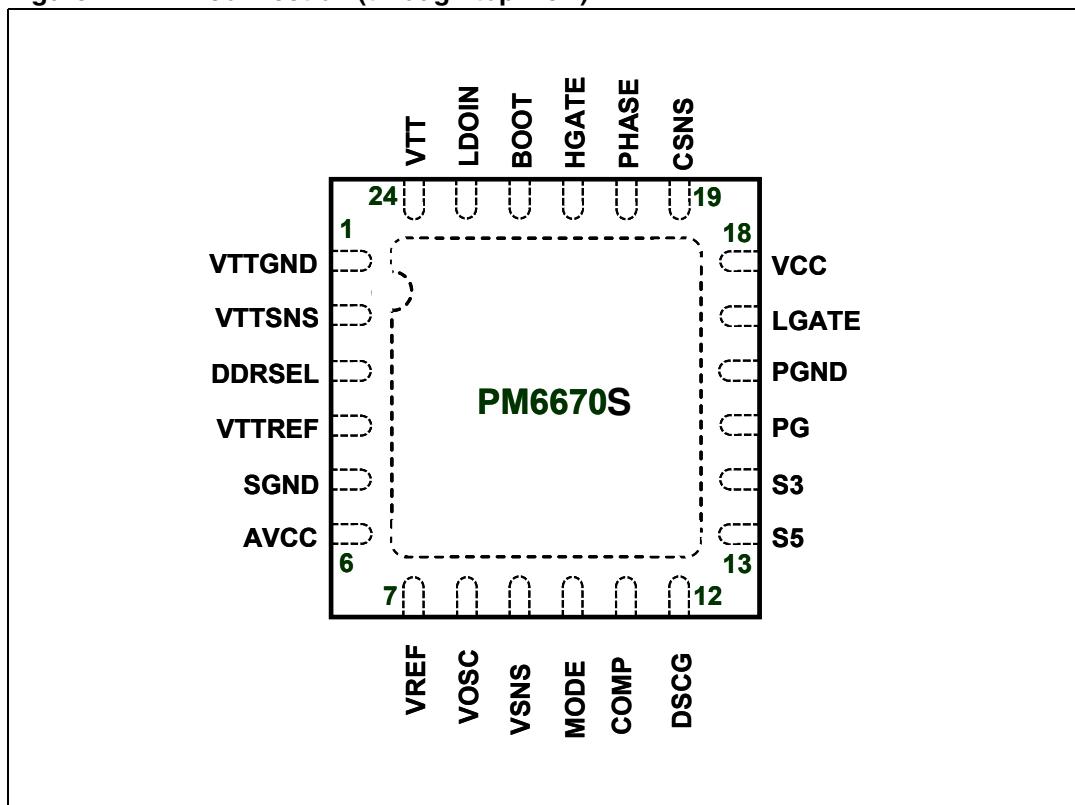

## 2 Pin settings

### 2.1 Connections

Figure 2. Pin connection (through top view)

## 2.2 Pin description

**Table 2. Pin functions**

| N° | Pin    | Function                                                                                                                                                                                                                                                                       |

|----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | VTTGND | LDO power ground. Connect to negative terminal of VTT output capacitor.                                                                                                                                                                                                        |

| 2  | VTTNS  | LDO remote sensing. Connect as close as possible to the load via a low noise PCB trace.                                                                                                                                                                                        |

| 3  | DDRSEL | DDR voltage selector (if MODE is tied to VCC) or pulse-skip/no-audible pulse-skip selector in adjustable mode (MODE voltage lower than 3 V). See <a href="#">Section 7.1.4: Mode-of-operation selection on page 30</a> .                                                       |

| 4  | VTTREF | Low noise buffered DDR reference voltage. A 22 nF (minimum) ceramic bypass capacitor is required in order to achieve stability.                                                                                                                                                |

| 5  | SGND   | Ground reference for analog circuitry, control logic and VTTREF buffer. Connect together with the thermal pad and VTTGND to a low impedance ground plane. See the <i>Application Note</i> for details.                                                                         |

| 6  | AVCC   | +5 V supply for internal logic. Connect to +5 V rail through a simple RC filtering network.                                                                                                                                                                                    |

| 7  | VREF   | High accuracy output voltage reference (1.237 V) for multilevel pins setting. It can deliver up to 50 $\mu$ A. Connect a 100 nF capacitor between VREF and SGND in order to enhance noise rejection.                                                                           |

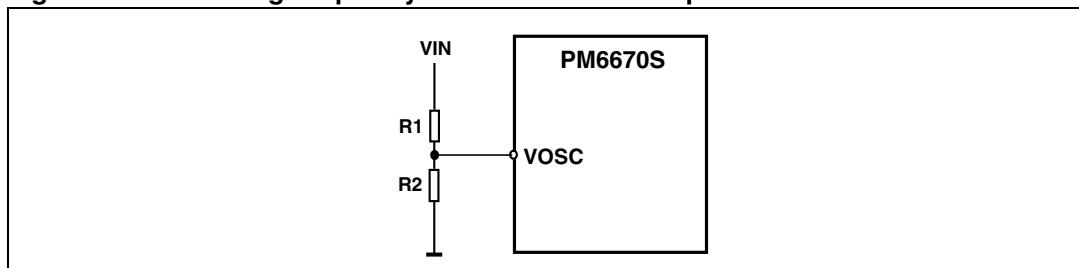

| 8  | VOSC   | Frequency selection. Connect to the central tap of a resistor divider to set the desired switching frequency. The pin cannot be left floating. See <a href="#">Section 7: Device description on page 20</a>                                                                    |

| 9  | VSNS   | VDDQ output remote sensing. Discharge path for VDDQ in Non-Tracking Discharge. Input for internal resistor divider that provides VDDQ/2 to VTTREF and VTT. Connect as close as possible to the load via a low noise PCB trace.                                                 |

| 10 | MODE   | Mode of operation selector. If MODE pin voltage is higher than 4 V, the fixed output mode is selected. If MODE pin voltage is lower than 4 V, it is used as negative input of the error amplifier. See <a href="#">Section 7.1.4: Mode-of-operation selection on page 30</a> . |

| 11 | COMP   | DC voltage error compensation Input for the switching section. Refer <a href="#">Section 7.1.4: Mode-of-operation selection on page 30</a> .                                                                                                                                   |

| 12 | DSCG   | Discharge mode selection. Refer to <a href="#">Section 7.1.8: VDDQ output discharge on page 34</a> for tracking/non-tracking discharge or no-discharge options.                                                                                                                |

| 13 | S5     | Switching controller enable. Connect to S5 system status signal to meet S0-S5 power management states compliance. See <a href="#">Section 7.3: S3 and S5 power management pins on page 38</a> , S5 pin can't be left floating.                                                 |

| 14 | S3     | Linear regulator enable. Connect to S3 system status signal to meet S0-S5 power management states compliance. See <a href="#">Section 7.3: S3 and S5 power management pins on page 38</a> , S3 pin can't be left floating.                                                     |

| 15 | PG     | Power Good signal (open drain output). High when VDDQ output voltage is within $\pm 10$ % of nominal value.                                                                                                                                                                    |

| 16 | PGND   | Power ground for the switching section.                                                                                                                                                                                                                                        |

| 17 | LGATE  | Low-side gate driver output.                                                                                                                                                                                                                                                   |

**Table 2. Pin functions (continued)**

| N° | Pin   | Function                                                                                                                                                                                                                                                               |

|----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18 | VCC   | +5 V low-side gate driver supply. Bypass with a 100 nF capacitor to PGND.                                                                                                                                                                                              |

| 19 | CSNS  | Current sense input for the switching section. This pin must be connected through a resistor to the drain of the synchronous rectifier ( $R_{DSon}$ sensing) to set the current limit threshold.                                                                       |

| 20 | PHASE | Switch node connection and return path for the high-side gate driver.                                                                                                                                                                                                  |

| 21 | HGATE | High-side gate driver output                                                                                                                                                                                                                                           |

| 22 | BOOT  | Bootstrap capacitor connection. Positive supply input of the high-side gate driver.                                                                                                                                                                                    |

| 23 | LDOIN | Linear regulator input. Connect to VDDQ in normal configuration or to a lower supply to reduce the power dissipation. A 10 $\mu$ F bypass ceramic capacitor is suggested for noise rejection enhancement. See <a href="#">Section 7: Device description on page 20</a> |

| 24 | VTT   | LDO linear regulator output. Bypass with a 20 $\mu$ F (2x10 $\mu$ F MLCC) filter capacitor.                                                                                                                                                                            |

## 3 Electrical data

### 3.1 Maximum rating

Table 3. Absolute maximum ratings <sup>(1)</sup>

| Symbol      | Parameter                                                           | Value                    | Unit |

|-------------|---------------------------------------------------------------------|--------------------------|------|

| $V_{AVCC}$  | AVCC to SGND                                                        | -0.3 to 6                | V    |

| $V_{VCC}$   | VCC to SGND                                                         | -0.3 to 6                |      |

|             | PGND, VTTGND to SGND                                                | -0.3 to 0.3              |      |

|             | HGATE and BOOT to PHASE                                             | -0.3 to 6                |      |

|             | HGATE and BOOT to PGND                                              | -0.3 to 44               |      |

| $V_{PHASE}$ | PHASE to SGND <sup>(2)</sup>                                        | -0.3 to 38               |      |

|             | LGATE to PGND                                                       | -0.3 to $V_{CC} + 0.3$   |      |

|             | CSNS, PG, S3, S5, DSCG, COMP, VSNS, VOSC, VREF, MODE, DDRSEL to GND | -0.3 to $V_{AVCC} + 0.3$ |      |

|             | VTTREF, VREF, VTT, VTTNS to SGND                                    | -0.3 to $V_{AVCC} + 0.3$ |      |

| $P_{TOT}$   | Power dissipation @ $T_A = 25^\circ\text{C}$                        | 2.3                      | W    |

1. Free air operating conditions unless otherwise specified. Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

2. PHASE to SGND up to -2.5 V for  $t < 10$  ns

### 3.2 Thermal data

Table 4. Thermal data

| Symbol     | Parameter                              | Value       | Unit |

|------------|----------------------------------------|-------------|------|

| $R_{thJA}$ | Thermal resistance junction to ambient | 42          | °C/W |

| $T_{STG}$  | Storage temperature range              | - 50 to 150 | °C   |

| $T_A$      | Operating ambient temperature range    | - 40 to 85  | °C   |

| $T_J$      | Junction operating temperature range   | - 40 to 125 | °C   |

### 3.3 Recommended operating conditions

Table 5. Recommended operating conditions

| Symbol     | Parameter           | Values |     |     | Unit |

|------------|---------------------|--------|-----|-----|------|

|            |                     | Min    | Typ | Max |      |

| $V_{IN}$   | Input voltage range | 4.5    | -   | 28  | V    |

| $V_{AVCC}$ | IC supply voltage   | 4.5    | -   | 5.5 |      |

| $V_{VCC}$  | IC supply voltage   | 4.5    | -   | 5.5 |      |

## 4 Electrical characteristics

$T_A = 0^\circ\text{C}$  to  $85^\circ\text{C}$ ,  $VCC = AVCC = +5\text{ V}$  and  $LDOIN$  connected to  $VDDQ$  output if not otherwise specified <sup>(a)</sup>

**Table 6. Electrical characteristics**

| Symbol                   | Parameter                                  | Test condition                                                                                      | Values        |       |       | Unit          |    |

|--------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------|-------|-------|---------------|----|

|                          |                                            |                                                                                                     | Min           | Typ   | Max   |               |    |

| <b>Supply section</b>    |                                            |                                                                                                     |               |       |       |               |    |

| $I_{IN}$                 | Operating current                          | S3, S5, MODE and DDRSEL connected to AVCC, no load on VTT and VTTREF outputs. VCC connected to AVCC |               | 0.8   | 2     | mA            |    |

| $I_{STR}$                | Operating current in STR                   | S5, MODE and DDRSEL connected to AVCC, S3 tied to SGND, no load on VTTREF. VCC connected to AVCC    |               | 0.6   | 1     |               |    |

| $I_{SH}$                 | Operating current in shutdown              | S3 and S5 tied to SGND. Discharge mode active. VCC connected to AVCC                                |               | 1     | 10    | $\mu\text{A}$ |    |

| UVLO                     | AVCC under voltage lockout upper threshold |                                                                                                     | 4.1           | 4.25  | 4.4   | V             |    |

|                          | AVCC under voltage lockout lower threshold |                                                                                                     | 3.85          | 4.0   | 4.1   |               |    |

|                          | UVLO hysteresis                            |                                                                                                     | 70            |       |       | mV            |    |

| <b>ON-time (SMPS)</b>    |                                            |                                                                                                     |               |       |       |               |    |

| $t_{ON}$                 | On-time duration                           | MODE and DDRSEL high, $V_{VSNS} = 2\text{ V}$                                                       | VOSC = 300 mV | 650   | 750   | 850           | ns |

|                          |                                            |                                                                                                     | VOSC = 500 mV | 390   | 450   | 510           |    |

| <b>OFF-time (SMPS)</b>   |                                            |                                                                                                     |               |       |       |               |    |

| $t_{OFFMIN}$             | Minimum Off time                           |                                                                                                     |               | 300   | 350   | ns            |    |

| <b>Voltage reference</b> |                                            |                                                                                                     |               |       |       |               |    |

|                          | Voltage accuracy                           | 4.5 V < $V_{IN}$ < 25 V                                                                             | 1.224         | 1.237 | 1.249 | V             |    |

|                          | Load regulation                            | $-50\text{ }\mu\text{A} < I_{VREF} < 50\text{ }\mu\text{A}$                                         | -4            |       | 4     | mV            |    |

|                          | Undervoltage lockout fault threshold       |                                                                                                     |               | 800   |       |               |    |

a.  $T_A = T_J$ . All parameters at operating temperature extremes are guaranteed by design and statistical analysis (not production tested)

Table 6. Electrical characteristics (continued)

| Symbol                                                   | Parameter                                    | Test condition                                                     | Values |     |     | Unit |

|----------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------|--------|-----|-----|------|

|                                                          |                                              |                                                                    | Min    | Typ | Max |      |

| <b>VDDQ output</b>                                       |                                              |                                                                    |        |     |     |      |

| V <sub>VDDQ</sub>                                        | VDDQ output voltage, DDR3                    | MODE connected to AVCC, DDRSEL tied to SGND, No load               |        | 1.5 |     | V    |

|                                                          | VDDQ output voltage, DDR2                    | MODE and DDRSEL connected to AVCC, no load                         |        | 1.8 |     |      |

|                                                          | Feedback accuracy                            |                                                                    | -1.5   |     | 1.5 | %    |

| <b>Current limit and zero crossing comparator</b>        |                                              |                                                                    |        |     |     |      |

| I <sub>CSNS</sub>                                        | CSNS input bias current                      |                                                                    | 110    | 120 | 130 | μA   |

|                                                          | Comparator offset                            |                                                                    | -6     |     | 6   | mV   |

|                                                          | Positive current limit threshold             | R <sub>sense</sub> = 1 kΩ<br>V <sub>PGND</sub> - V <sub>CSNS</sub> |        | 120 |     | mV   |

|                                                          | Fixed negative current limit threshold       |                                                                    |        | 110 |     | mV   |

| V <sub>ZC,OFFS</sub>                                     | Zero crossing comparator offset              |                                                                    | -11    | -5  | 1   | mV   |

| <b>High and low side gate drivers</b>                    |                                              |                                                                    |        |     |     |      |

|                                                          | HGATE driver on-resistance                   | HGATE high state (pull-up)                                         |        | 2.0 | 3   | Ω    |

|                                                          |                                              | HGATE low state (pull-down)                                        |        | 1.8 | 2.7 |      |

|                                                          | LGATE driver on-resistance                   | LGATE high state (pull-up)                                         |        | 1.4 | 2.1 |      |

|                                                          |                                              | LGATE low state (pull-down)                                        |        | 0.6 | 0.9 |      |

| <b>UV/P/OVP protections and PGOOD SIGNAL (SMPS only)</b> |                                              |                                                                    |        |     |     |      |

| OVP                                                      | Over voltage threshold                       |                                                                    | 112    | 115 | 118 | %    |

| UV                                                       | Under voltage threshold                      |                                                                    | 67     | 70  | 73  |      |

| PGOOD                                                    | Power Good upper threshold                   |                                                                    | 107    | 110 | 113 |      |

|                                                          | Power Good lower threshold                   |                                                                    | 86     | 90  | 93  |      |

| I <sub>PG,LEAK</sub>                                     | PG leakage current                           | PG forced to 5 V                                                   |        |     | 1   | μA   |

| V <sub>PG,LOW</sub>                                      | PG low-level voltage                         | I <sub>PG,SINK</sub> = 4 mA                                        |        | 150 | 250 | mV   |

| <b>Soft start section (SMPS)</b>                         |                                              |                                                                    |        |     |     |      |

|                                                          | Soft-start ramp time (4 steps current limit) |                                                                    | 1.5    | 3   | 4   | ms   |

|                                                          | Soft-start current limit step                |                                                                    |        | 30  |     | μA   |

Table 6. Electrical characteristics (continued)

| Symbol                            | Parameter                                                                                 | Test condition                                                    | Values |      |     | Unit |

|-----------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------|------|-----|------|

|                                   |                                                                                           |                                                                   | Min    | Typ  | Max |      |

| <b>Soft end section</b>           |                                                                                           |                                                                   |        |      |     |      |

|                                   | VDDQ discharge resistance in non-tracking discharge mode                                  |                                                                   | 15     | 25   | 35  | Ω    |

|                                   | VTT discharge resistance in non-tracking discharge mode                                   |                                                                   | 15     | 25   | 35  |      |

|                                   | VTTREF discharge resistance in non-tracking discharge mode                                |                                                                   | 1      | 1.5  | 2   | kΩ   |

|                                   | VDDQ output threshold synchronous for final tracking to non-tracking discharge transition |                                                                   | 0.2    | 0.4  | 0.6 | V    |

| <b>V<sub>TT</sub> LDO section</b> |                                                                                           |                                                                   |        |      |     |      |

| I <sub>LDOIN,ON</sub>             | LDO input bias current in full-on state                                                   | S3 = S5 = +5 V, No load on VTT                                    |        | 1    | 10  | μA   |

| I <sub>LDOIN,STR</sub>            | LDO input bias current in suspend-to-RAM state                                            | S3 = 0 V, S5 = +5 V, No Load on VTT                               |        |      | 10  |      |

| I <sub>LDOIN,STD</sub>            | LDO input bias current in suspend-to-disk state                                           | S3 = S5 = 0 V, No Load on VTT                                     |        |      | 1   |      |

| I <sub>VTTSNS,BIAS</sub>          | VTTSNS bias current                                                                       | S3 = +5 V, S5 = +5 V, V <sub>VTTSNS</sub> = V <sub>VSNS</sub> /2  |        |      | 1   |      |

| I <sub>VTTSNS,LEAK</sub>          | VTTSNS leakage current                                                                    | S3 = 0 V, S5 = +5 V, V <sub>VTTSNS</sub> = V <sub>VSNS</sub> /2   |        |      | 1   |      |

| I <sub>VTT,LEAK</sub>             | VTT leakage current                                                                       | S3 = 0 V, S5 = +5 V, V <sub>VTT</sub> = V <sub>VSNS</sub> /2      | -10    |      | 10  |      |

| V <sub>VTT</sub>                  | LDO linear regulator output voltage (DDR2)                                                | S3 = S5 = +5 V, I <sub>VTT</sub> = 0 A, MODE = DDRSEL = +5 V      |        | 0.9  |     | V    |

|                                   | LDO linear regulator output voltage (DDR3)                                                | S3 = S5 = +5 V, I <sub>VTT</sub> = 0 A, MODE = +5 V, DDRSEL = 0 V |        | 0.75 |     |      |

|                                   | LDO output accuracy respect to VTTREF                                                     | S3 = S5 = MODE = + 5 V, -1 mA < I <sub>VTT</sub> < 1 mA           | -20    |      | 20  | mV   |

|                                   |                                                                                           | S3 = S5 = MODE = +5 V, -1 A < I <sub>VTT</sub> < 1 A              | -25    |      | 25  |      |

|                                   |                                                                                           | S3 = S5 = MODE = +5 V, -2 A < I <sub>VTT</sub> < 2 A              | -35    |      | 35  |      |

Table 6. Electrical characteristics (continued)

| Symbol                          | Parameter                                        | Test condition                                                  | Values                 |       |                        | Unit |

|---------------------------------|--------------------------------------------------|-----------------------------------------------------------------|------------------------|-------|------------------------|------|

|                                 |                                                  |                                                                 | Min                    | Typ   | Max                    |      |

| I <sub>VTT,CL</sub>             | LDO source current limit                         | V <sub>VTT</sub> < 1.10*(V <sub>VSNS</sub> /2)                  | 2                      | 2.3   | 3                      | A    |

|                                 |                                                  | V <sub>VTT</sub> > 1.10*(V <sub>VSNS</sub> /2)                  | 1                      | 1.15  | 1.4                    |      |

|                                 | LDO sink current limit                           | V <sub>VTT</sub> > 0.90*(V <sub>VSNS</sub> /2)                  | -3                     | -2.3  | -2                     |      |

|                                 |                                                  | V <sub>VTT</sub> < 0.90*(V <sub>VSNS</sub> /2)                  | -1.4                   | -1.15 | -1                     |      |

| <b>VTTREF section</b>           |                                                  |                                                                 |                        |       |                        |      |

| V <sub>VTTREF</sub>             | VTTREF output voltage                            | I <sub>VTTREF</sub> = 0 A, V <sub>VSNS</sub> = 1.8 V            |                        | 0.9   |                        | V    |

|                                 | VTTREF output voltage accuracy respect to VSNS/2 | -15 mA < I <sub>VTTREF</sub> < 15 mA, V <sub>VSNS</sub> = 1.8 V | -2                     |       | 2                      | %    |

| I <sub>VTTREF</sub>             | VTTREF current limit                             | VTTREF= 0 or VSNS                                               |                        | ±40   |                        | mA   |

| <b>Power management section</b> |                                                  |                                                                 |                        |       |                        |      |

| S3,S5                           | Turn OFF level                                   |                                                                 | 0.4                    |       |                        | V    |

|                                 | Turn ON level                                    |                                                                 |                        |       | 1.6                    |      |

| V <sub>MODE</sub>               | MODE pin high level threshold                    |                                                                 | V <sub>AVCC</sub> -0.7 |       |                        |      |

|                                 | MODE pin low level threshold                     |                                                                 |                        |       | V <sub>AVCC</sub> -1.3 |      |

| V <sub>DDRSEL</sub>             | DDRSEL pin high level threshold                  |                                                                 | V <sub>AVCC</sub> -0.8 |       |                        |      |

|                                 | DDRSEL pin middle level window                   |                                                                 |                        | 1.0   | V <sub>AVCC</sub> -1.5 |      |

|                                 | DDRSEL pin low level threshold                   |                                                                 |                        |       | 0.5                    |      |

| V <sub>DSCG</sub>               | DSCG pin high level threshold                    |                                                                 | V <sub>AVCC</sub> -0.8 |       |                        |      |

|                                 | DSCG pin middle level window                     |                                                                 |                        | 1.0   | 2.0                    |      |

|                                 | DSCG pin low level threshold                     |                                                                 |                        |       | 0.5                    |      |

| I <sub>IN,LEAK</sub>            | Logic inputs leakage current                     | S3, S5 = 5 V                                                    |                        |       | 10                     | μA   |

| I <sub>IN3,LEAK</sub>           | Multilevel inputs leakage current                | MODE, DDRSEL and DSCG = 5 V                                     |                        |       | 10                     |      |

| I <sub>OSC, LEAK</sub>          | VOSC input leakage current                       | VOSC = 500 mV                                                   |                        |       | 1                      |      |

| <b>Thermal shutdown</b>         |                                                  |                                                                 |                        |       |                        |      |

| T <sub>SHDN</sub>               | Shutdown temperature (1)                         |                                                                 |                        | 150   |                        | °C   |

1. Guaranteed by design. Not production tested.

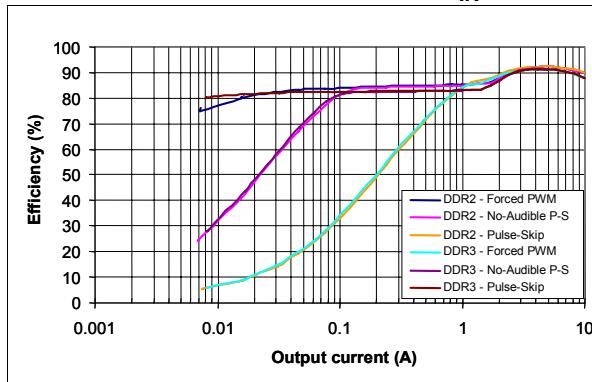

## 5 Typical operating characteristics

**Figure 3. Efficiency vs load - 1.5 V and 1.8 V,  $V_{IN} = 12$  V**

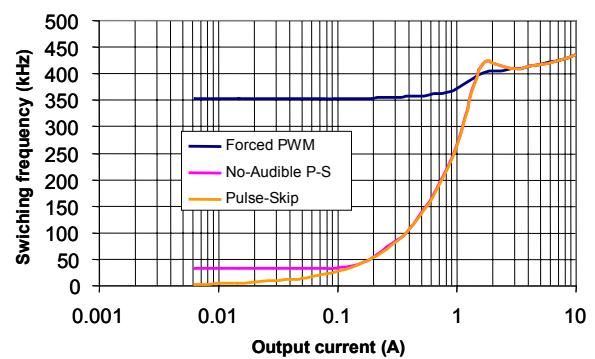

**Figure 4. Switching frequency vs load - 1.8 V,  $V_{IN} = 12$  V**

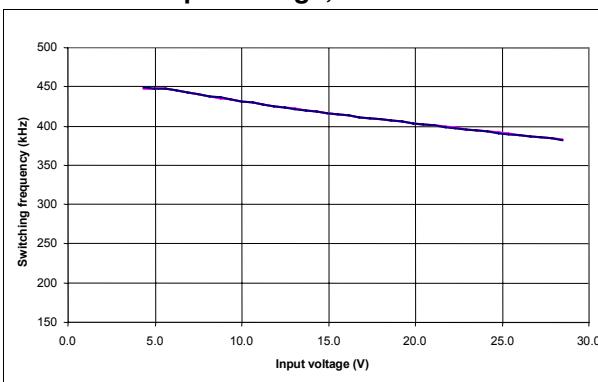

**Figure 5. Switching frequency vs input voltage, 1.8 V**

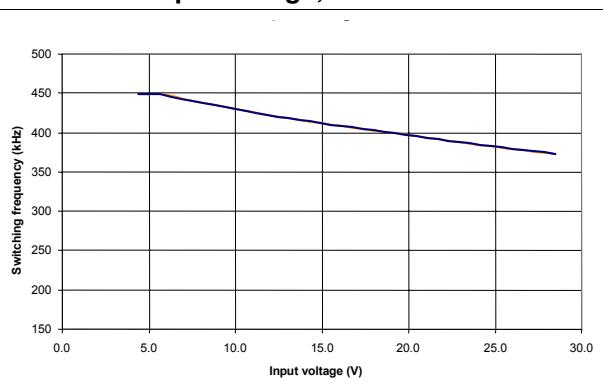

**Figure 6. Switching frequency vs input voltage, 1.5 V**

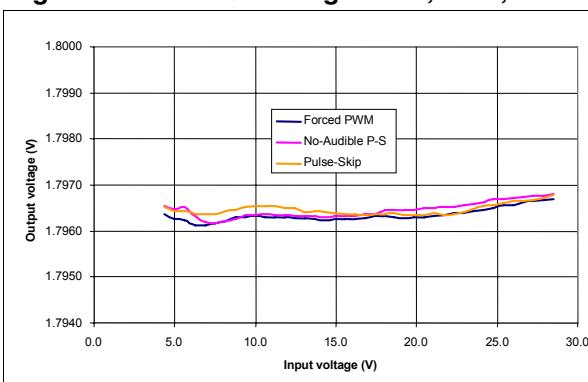

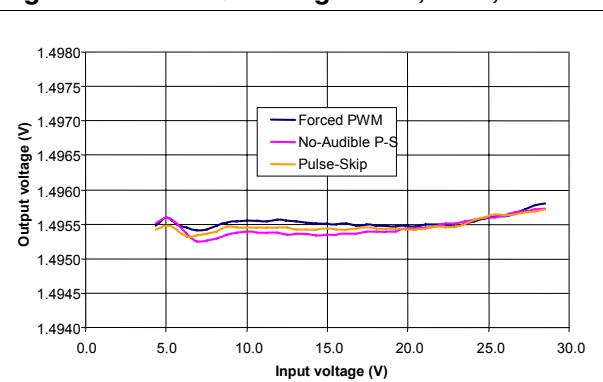

**Figure 7. VDDQ line regulation, 1.8 V, 7 A**

**Figure 8. VDDQ line regulation, 1.5 V, 7 A**

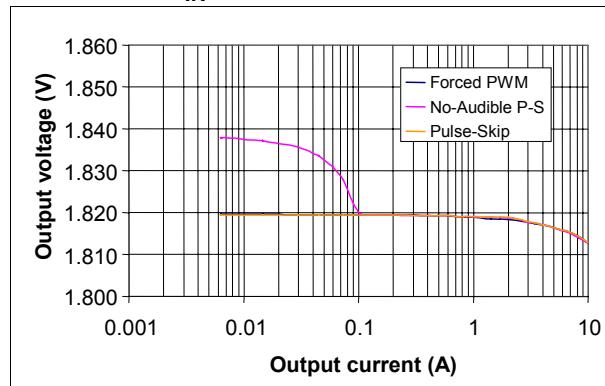

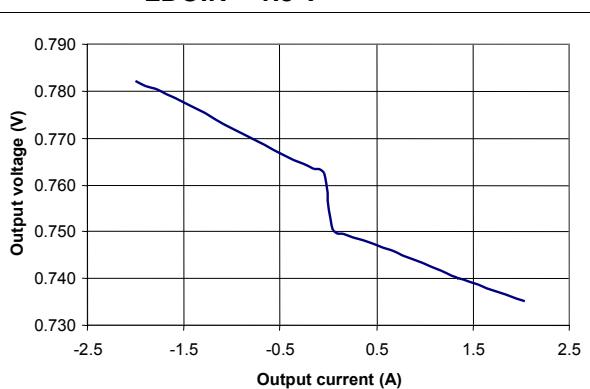

**Figure 9. VDDQ load regulation, 1.8 V,  $V_{IN} = 12$  V**

**Figure 10. VDDQ load regulation, 1.5 V,  $V_{IN} = 12$  V**

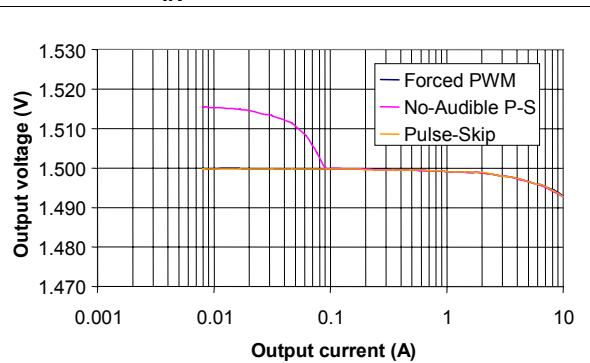

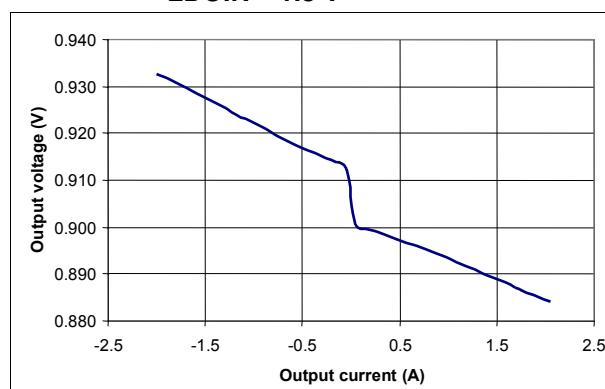

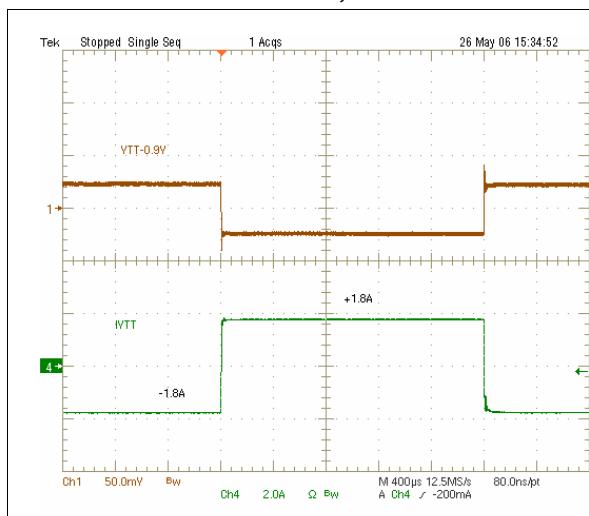

**Figure 11. VTT load regulation, 0.9 V, LDOIN = 1.8 V**

**Figure 12. VTT load regulation, 0.75 V, LDOIN = 1.5 V**

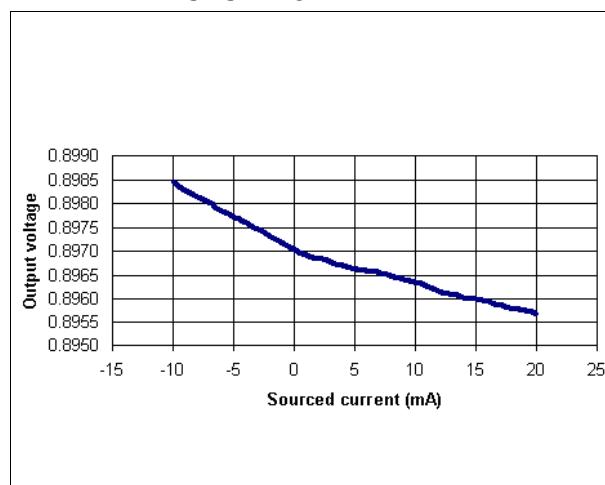

**Figure 13. VTTREF load regulation, 0.9 V, VSNS = 1.8 V**

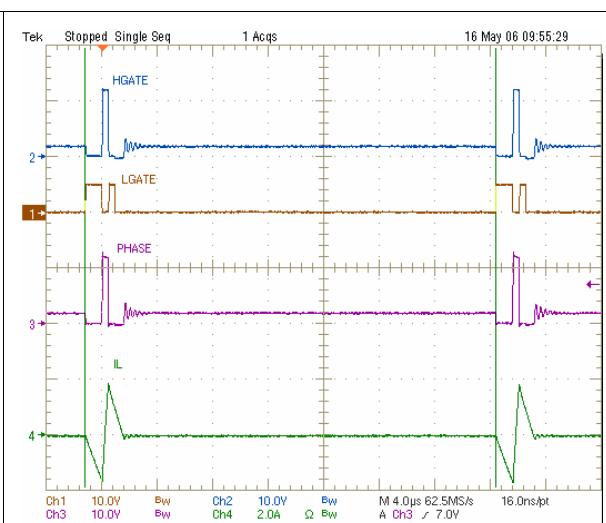

**Figure 14. No-audible pulse-skip waveforms**

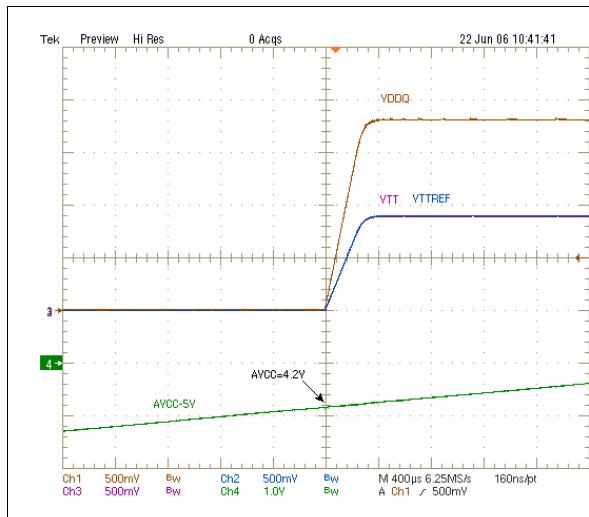

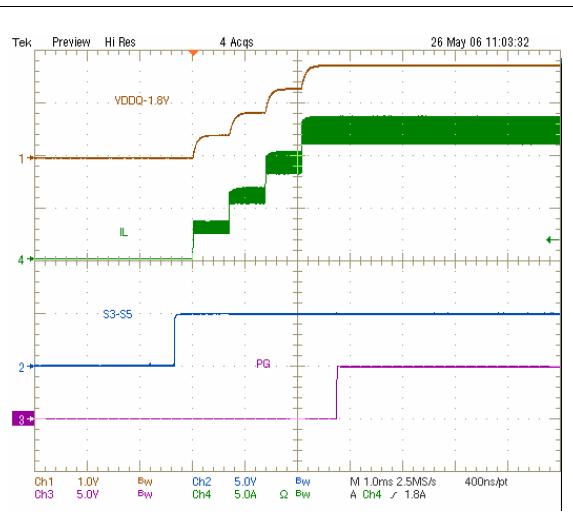

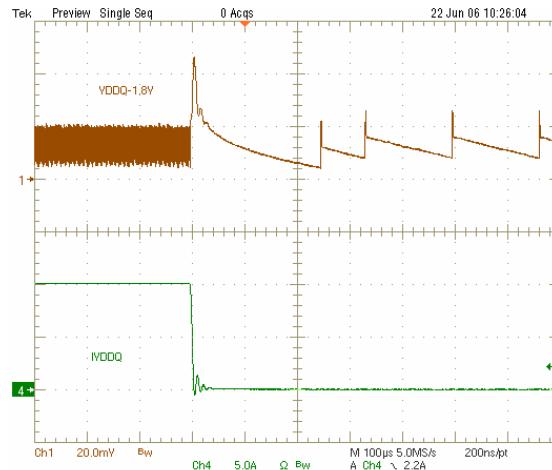

**Figure 15. Power-up sequence - AVCC above UVLO****Figure 17. -1.8 A to 1.8 A VTT load transient, 0.9 V****Figure 16. VDDQ soft-start, 1.8 V, heavy load****Figure 18. 0 mA to 9 mA VTTREF load transient, 0.9 V**

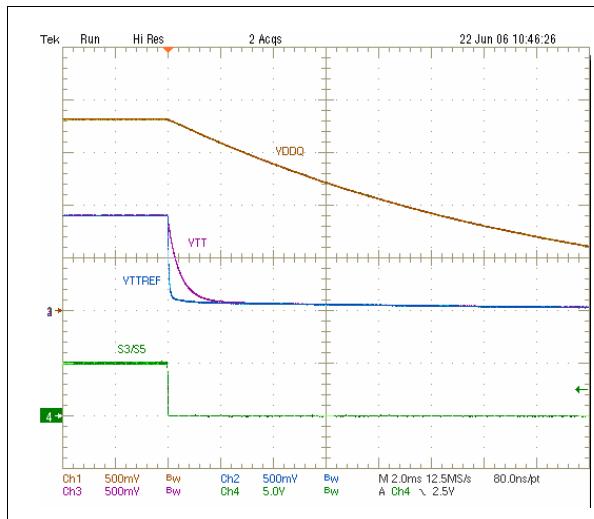

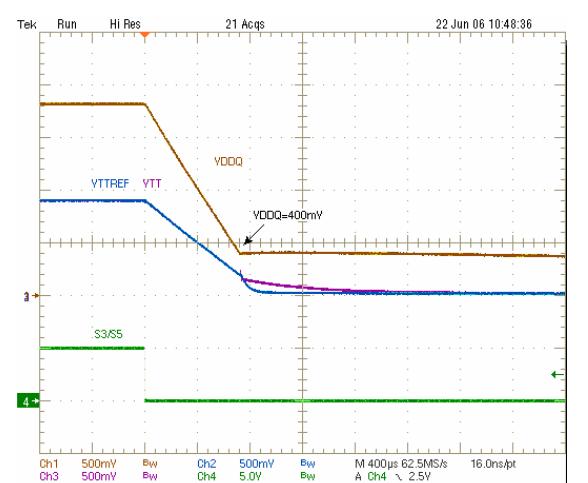

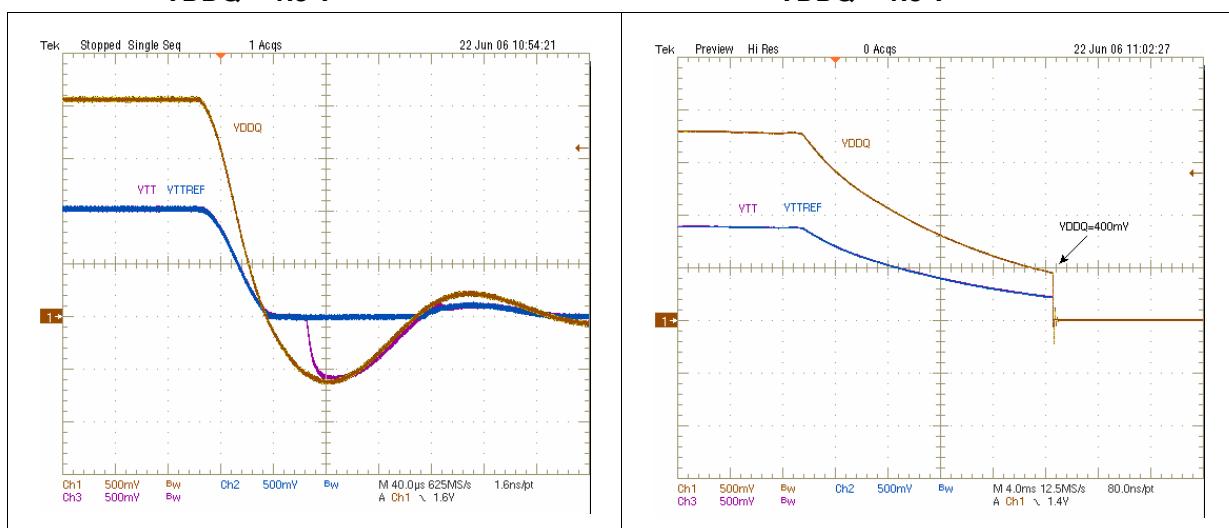

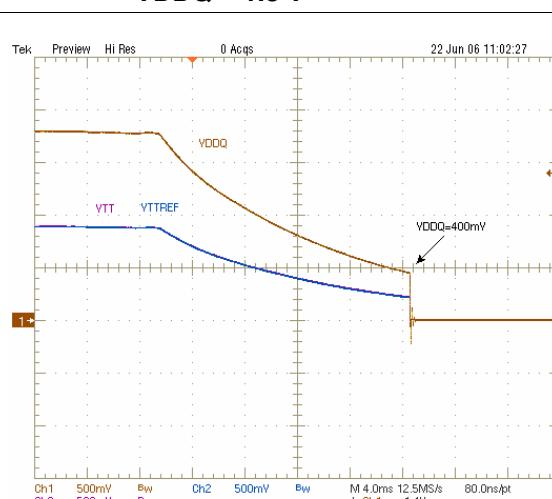

Figure 19. Non-tracking (soft) discharge

Figure 20. Tracking (fast) discharge, LDOIN = VDDQ

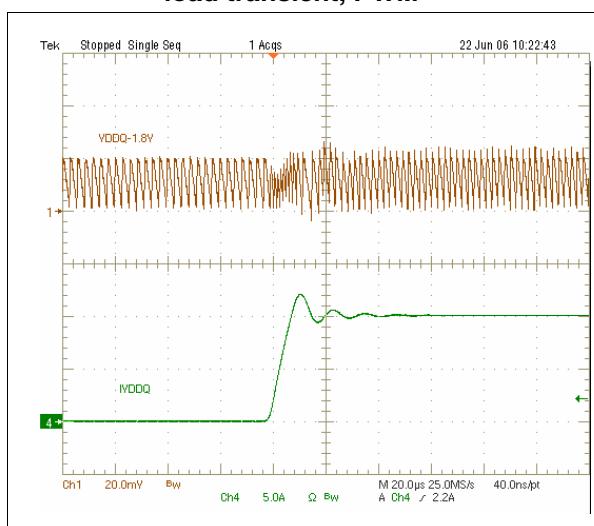

Figure 21. 0 A to 10 A VDDQ load transient, PWM

Figure 22. 10 A to 0 A VDDQ load transient, PWM

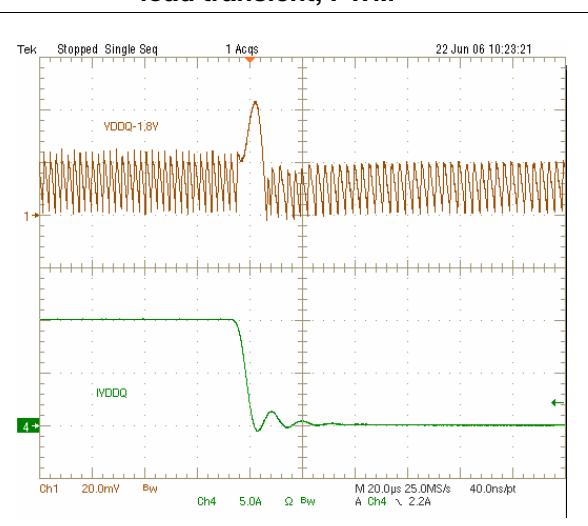

**Figure 23. 0 A to 10 A VDDQ

load transient, pulse-skip**

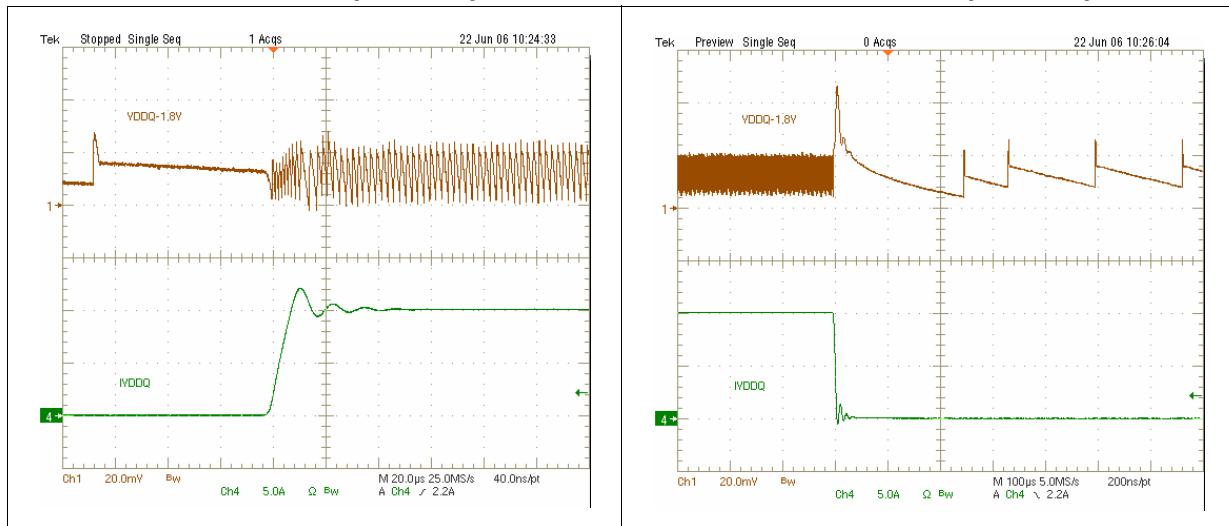

**Figure 25. Over-voltage protection,

VDDQ = 1.8 V**

**Figure 24. 10 A to 0 A VDDQ

load transient, pulse-skip**

**Figure 26. Under-voltage protection,

VDDQ = 1.8 V**

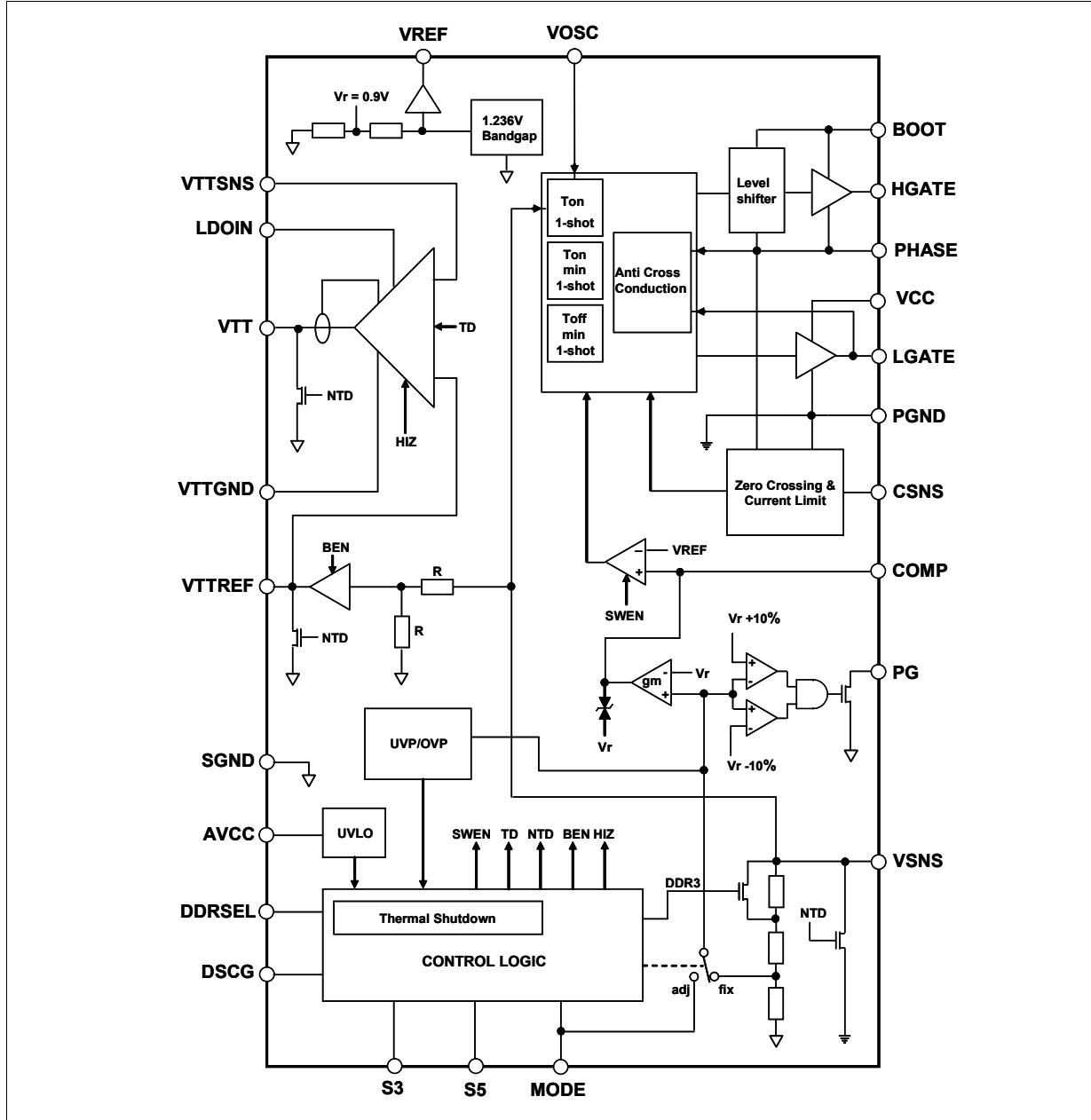

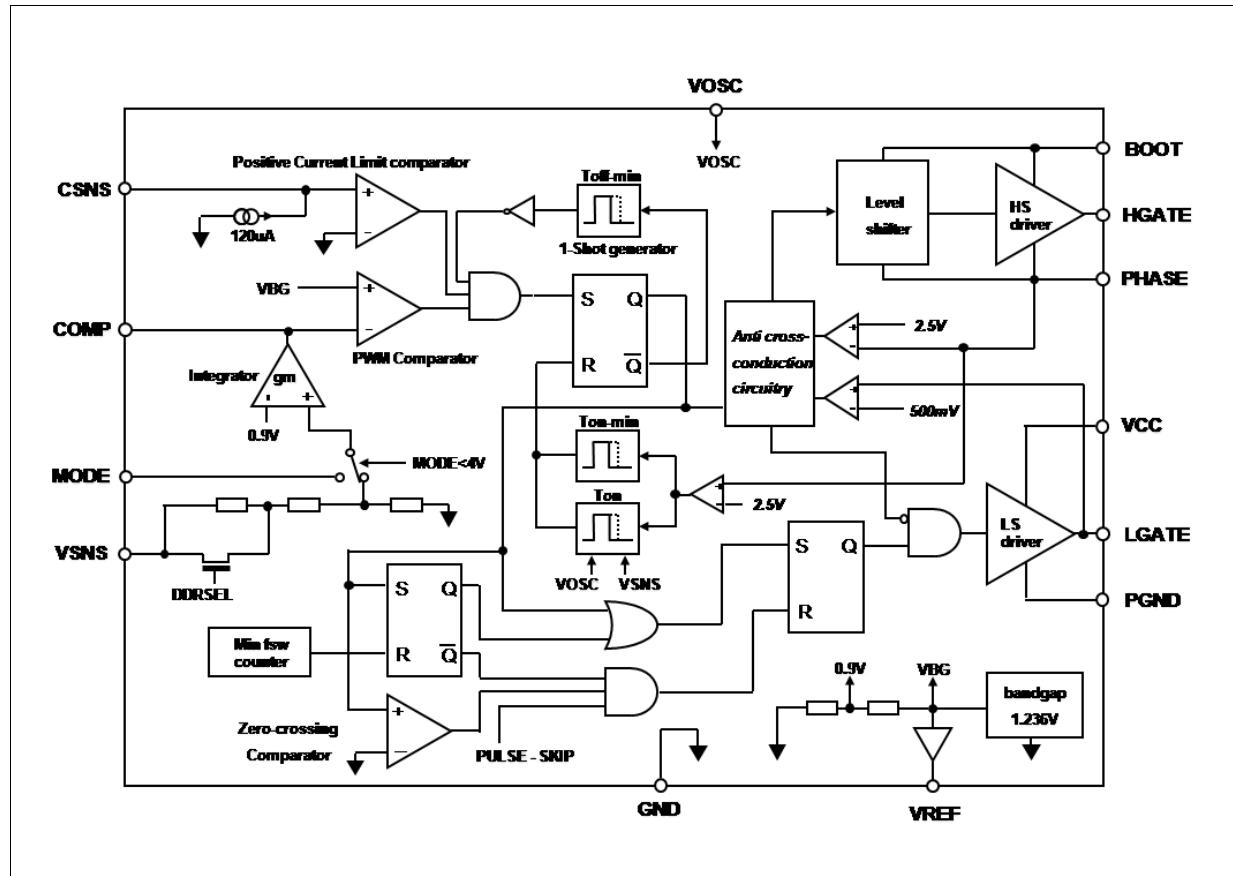

## 6 Block diagram

**Figure 27. Functional and block diagram**

**Table 7. Legend**

|      |                                |

|------|--------------------------------|

| SWEN | Switching controller enable    |

| TD   | Tracking discharge enable      |

| NTD  | Non-tracking discharge enable  |

| BEN  | VTTREF buffer enable           |

| HIZ  | LDO high impedance mode enable |

## 7 Device description

The PM6670SS is designed to satisfy DDR2-3 power supply requirements combining a synchronous buck controller, a 15 mA buffered reference and a high-current low-drop out (LDO) linear regulator capable of sourcing and sinking up to 2 A<sub>pk</sub>. The switching controller section is a high-performance, pseudo-fixed frequency, constant-on-time (COT) based regulator specifically designed for handling fast load transient over a wide range of input voltages.

The DDR2-3 supply voltage VDDQ can be easily set to 1.8 V (DDR2) or 1.5 V (DDR3) without additional components. The output voltage can also be adjusted in the 0.9 V to 2.6 V range using an external resistor divider. The switching mode power supply (SMPS) can handle different modes of operation in order to minimize noise or power consumption, depending on the application needs.

A lossless current sensing scheme, based on the Low-Side MOSFET's on resistance avoids the need for an external current sense resistor.

The output of the linear regulator (VTT) tracks the memory's reference voltage VTTREF within  $\pm 30$  mV over the full operating load conditions. The input of the LDO can be either VDDQ or a lower voltage rail in order to reduce the total power dissipation. Linear regulator stability is achieved by filtering its output with a ceramic capacitor (20  $\mu$ F or greater).

The reference voltage (VTTREF) section provides a voltage equal to one half of VSNS with an accuracy of 1 %. This regulator can source and sink up to  $\pm 15$  mA. A 10 nF to 100 nF bypass capacitor is required between VTTREF and SGND for stability.

According to DDR2/3 JEDEC specifications, when the system enters the suspend-to-RAM state the LDO output is left in high impedance while VTTREF and VDDQ are still alive. When the suspend-to-disk state (S3 and S5 tied to ground) is entered, all outputs are actively discharged when either tracking or non-tracking discharge is selected.

## 7.1 VDDQ section - constant on-time PWM controller

The PM6670S uses a pseudo-fixed frequency, constant on-time (COT) controller as the core of the switching section. It is well known that the COT controller uses a relatively simple algorithm and uses the ripple voltage derived across the output capacitor's ESR to trigger the on-time one-shot generator. In this way, the output capacitor's ESR acts as a current sense resistor providing the appropriate ramp signal to the PWM comparator. Nearly constant switching frequency is achieved by the system's loop in steady-state operating conditions by varying the on-time duration, avoiding thus the need for a clock generator. The on-time one shot duration is directly proportional to the output voltage, sensed at VSNS pin, and inversely proportional to the input voltage, sensed at the VOSC pin, as follows:

### Equation 1

$$T_{ON} = K_{OSC} \frac{V_{SNS}}{V_{OSC}} + \tau$$

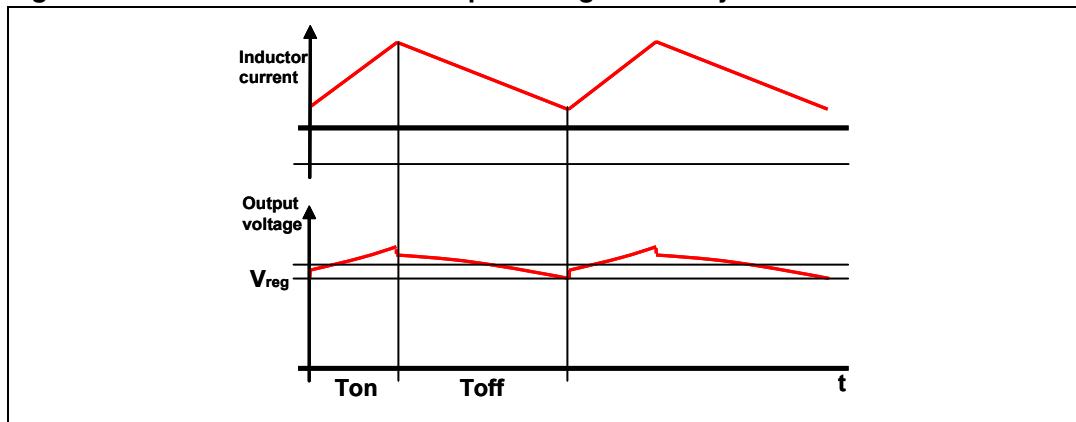

where  $K_{OSC}$  is a constant value (130 ns typ.) and  $\tau$  is the internal propagation delay (40ns typ.). The one-shot generator directly drives the high-side MOSFET at the beginning of each switching cycle allowing the inductor current to increase; after the on-time has expired, an Off-Time phase, in which the low-side MOSFET is turned on, follows. The off-time duration is solely determined by the output voltage: when lower than the set value (i.e. the voltage at VSNS pin is lower than the internal reference  $V_R = 0.9$  V), the synchronous rectifier is turned off and a new cycle begins ([Figure 28](#)).

**Figure 28. Inductor current and output voltage in steady state conditions**

The duty-cycle of the buck converter is, in steady-state conditions, given by

**Equation 2**

$$D = \frac{V_{OUT}}{V_{IN}}$$

The switching frequency is thus calculated as

**Equation 3**

$$f_{SW} = \frac{D}{T_{ON}} = \frac{\frac{V_{OUT}}{V_{IN}}}{K_{OSC} \frac{V_{SNS}}{V_{OSC}}} = \frac{\alpha_{OSC}}{\alpha_{OUT}} \cdot \frac{1}{K_{OSC}}$$

where

**Equation 4a**

$$\alpha_{OSC} = \frac{V_{OSC}}{V_{IN}}$$

**Equation 4b**

$$\alpha_{OUT} = \frac{V_{SNS}}{V_{OUT}}$$

Referring to the typical application schematic (figures on cover page and [Figure 29](#)), the final expression is then:

**Equation 5**

$$f_{SW} = \frac{\alpha_{OSC}}{K_{OSC}} = \frac{R_2}{R_1 + R_2} \cdot \frac{1}{K_{OSC}}$$

Even if the switching frequency is theoretically independent from battery and output voltages, parasitic parameters involved in power path (like MOSFETs' on-resistance and inductor's DCR) introduce voltage drops responsible for slight dependence on load current. In addition, the internal delay is due to a small dependence on input voltage. The PM6670S switching frequency can be set by an external divider connected to the VOSC pin.

**Figure 29. Switching frequency selection and VOSC pin**

The suggested voltage range for VOSC pin is 0.3 V to 2 V, for better switching frequency programmability.

### 7.1.1 Constant-on-time architecture

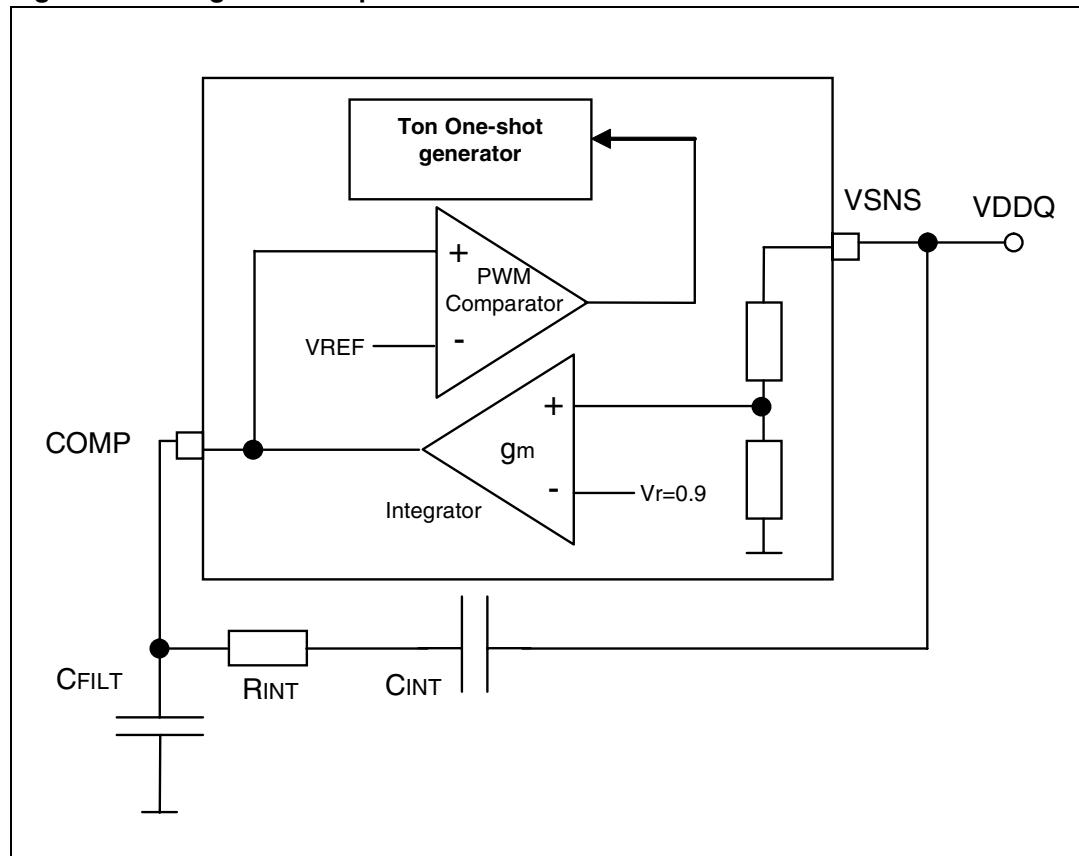

Figure 30 shows the simplified block diagram of the constant-on-time controller.

The switching regulator of the PM6670S owns a one-shot generator that ignites the high-side MOSFET when the following conditions are simultaneously satisfied: the PWM comparator is high (i.e. output voltage is lower than  $V_r = 0.9$  V), the synchronous rectifier current is below the current limit threshold and the minimum off-time has expired.

A minimum off-time constraint (300 ns typ.) is introduced to assure the boot capacitor charge and allow inductor valley current sensing on low-side MOSFET. A minimum on-time is also introduced to assure the start-up switching sequence.

Once the on-time has timed out, the high side switch is turned off, while the synchronous rectifier is ignited according to the anti-cross conduction management circuitry.

When the output voltage reaches the valley limit (determined by internal reference  $V_r = 0.9$  V), the low-side MOSFET is turned off according to the anti-cross conduction logic once again, and a new cycle begins.

Figure 30. Switching section simplified block diagram

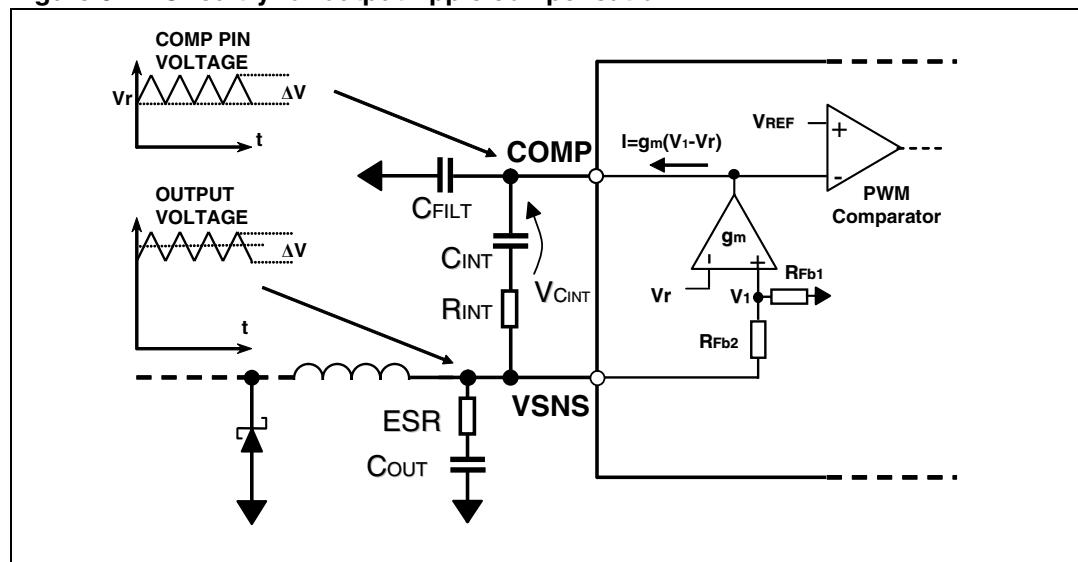

### 7.1.2 Output ripple compensation and loop stability

The loop is closed connecting the center tap of the output divider (internally, when the fixed output voltage is chosen, or externally, using the MODE pin in the adjustable output voltage mode). The feedback node is the negative input of the error comparator, while the positive input is internally connected to the reference voltage ( $V_r = 0.9$  V). When the feedback voltage becomes lower than the reference voltage, the PWM comparator goes to high and sets the control logic, turning on the high-side MOSFET. After the on-time (calculated as previously described) the system releases the high-side MOSFET and turns on the synchronous rectifier.

The voltage drop along ground and supply PCB paths, used to connect the output capacitor to the load, is a source of DC error. Furthermore the system regulates the output voltage valley, not the average, as shown in [Figure 28](#). Thus, the voltage ripple on the output capacitor is an additional source of DC error. To compensate this error, an integrative network is introduced in the control loop, by connecting the output voltage to the COMP pin through a capacitor ( $C_{INT}$ ) as shown in [Figure 31](#).

**Figure 31. Circuitry for output ripple compensation**

The additional capacitor is used to reduce the voltage on the COMP pin when higher than 300 mVpp and is unnecessary for most of applications. The trans conductance amplifier (gm) generates a current, proportional to the DC error, used to charge the CINT capacitor. The voltage across the CINT capacitor feeds the negative input of the PWM comparator, forcing the loop to compensate the total static error. An internal voltage clamp forces the COMP pin voltage range to  $\pm 150$  mV with respect to VREF. This is useful to avoid or smooth output voltage overshoot during a load transient. When the pulse-skip mode is entered, the clamping range is automatically reduced to 60 mV in order to enhance the recovering capability. In the ripple amplitude is larger than 150 mV, an additional capacitor CFILT can be connected between the COMP pin and ground to reduce ripple amplitude, otherwise the integrator will operate out of its linearity range. This capacitor is unnecessary for most of applications and can be omitted.

The design of the external feedback network depends on the output voltage ripple. If the ripple is higher than approximately 20 mV, the correct CINT capacitor is usually enough to keep the loop stable. The stability of the system depends firstly on the output capacitor zero frequency.

The following condition must be satisfied:

**Equation 6**

$$f_{SW} > k \cdot f_{Zout} = \frac{k}{2\pi \cdot C_{out} \cdot ESR}$$

where  $k$  is a fixed design parameter ( $k > 3$ ). It determines the minimum integrator capacitor value:

**Equation 7**

$$C_{INT} > \frac{g_m}{2\pi \cdot \left( \frac{f_{SW}}{k} - f_{Zout} \right)} \cdot \frac{Vr}{V_{out}}$$

where  $g_m = 50 \mu\text{s}$  is the integrator trans conductance.

In order to ensure stability it must be also verified that:

**Equation 8**

$$C_{INT} > \frac{g_m}{2\pi \cdot f_{Zout}} \cdot \frac{Vr}{V_{OUT}}$$

If the ripple on the COMP pin is greater than the integrator 150 mV, the auxiliary capacitor  $C_{FILT}$  can be added. If  $q$  is the desired attenuation factor of the output ripple,  $C_{FILT}$  is given by:

**Equation 9**

$$C_{FILT} = \frac{C_{INT} \cdot (1 - q)}{q}$$

In order to reduce the noise on the COMP pin, it is possible to add a resistor  $R_{INT}$  that, together with  $C_{INT}$  and  $C_{FILT}$ , becomes a low pass filter. The cutoff frequency  $f_{CUT}$  must be much greater (10 or more times) than the switching frequency:

**Equation 10**

$$R_{INT} = \frac{1}{2\pi \cdot f_{CUT} \cdot \frac{C_{INT} \cdot C_{FILT}}{C_{INT} + C_{FILT}}}$$

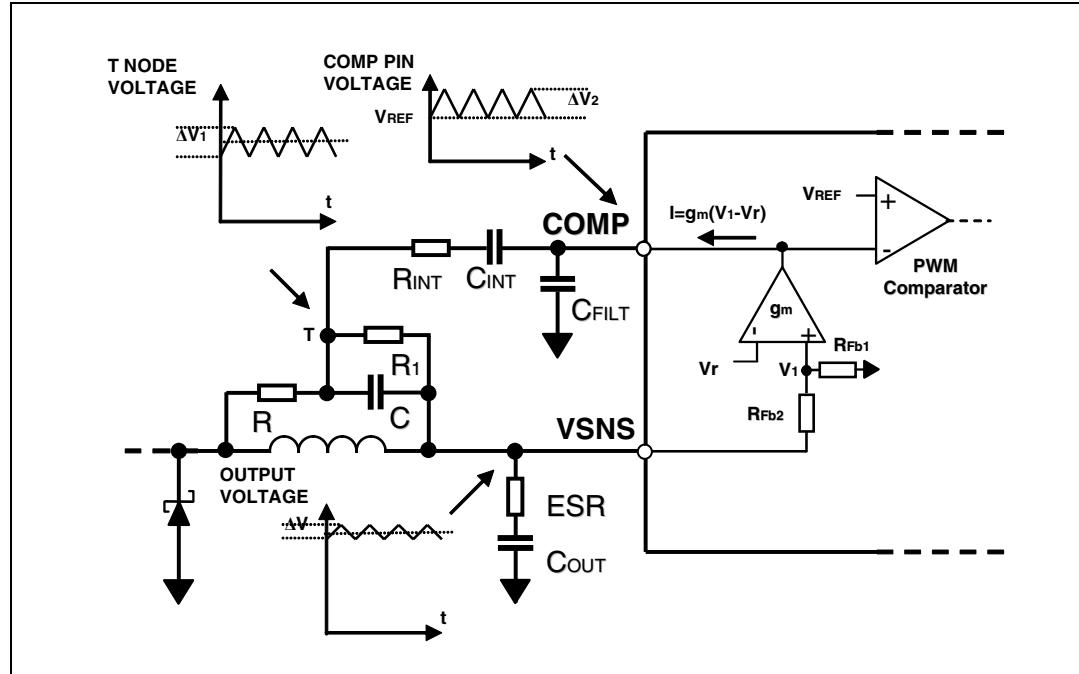

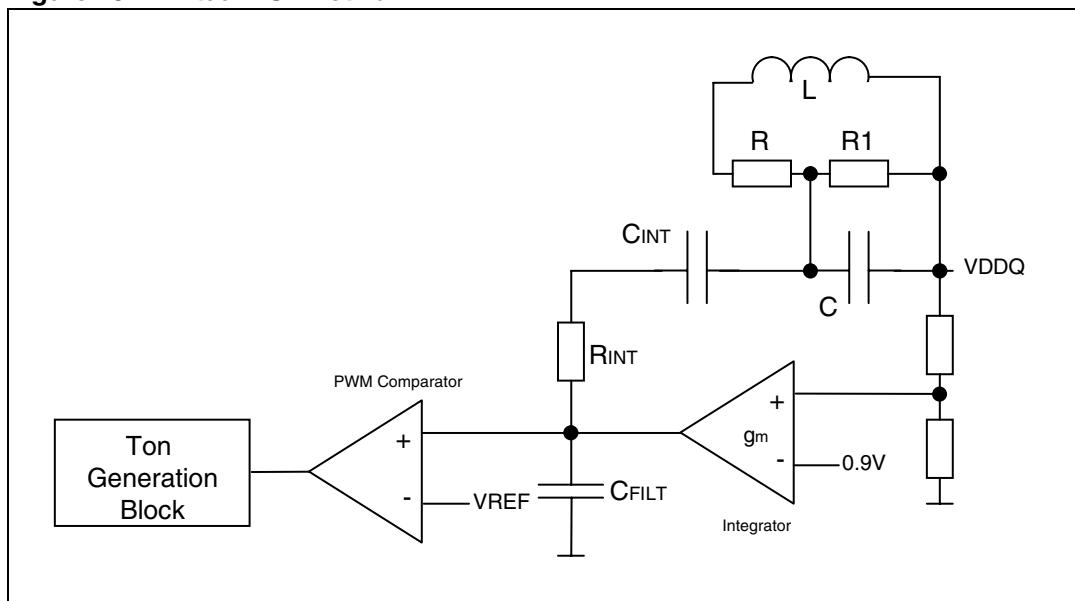

If the ripple is very small (lower than approximately 20 mV), a different compensation network, called "Virtual-ESR" network, is needed. This additional circuit generates a triangular ripple that is added to the output voltage ripple at the input of the integrator. The complete control scheme is shown in [Figure 32](#).

Figure 32. "Virtual-ESR" network

The ripple on the COMP pin is the sum of the output voltage ripple and the triangular ripple generated by the Virtual-ESR network. In fact the Virtual-ESR Network behaves like a another equivalent series resistor  $R_{VESR}$ .

A good trade-off is to design the network in order to achieve an  $R_{VESR}$  given by:

Equation 11

$$R_{VESR} = \frac{V_{RIPPLE}}{\Delta I_L} - ESR$$

where  $\Delta I_L$  is the inductor current ripple and  $V_{RIPPLE}$  is the total ripple at the T node, chosen greater than approximately 20 mV.

The new closed-loop gain depends on  $C_{INT}$ . In order to ensure stability it must be verified that:

Equation 12

$$C_{INT} > \frac{g_m}{2\pi \cdot f_z} \cdot \frac{V_r}{V_{out}}$$

where:

Equation 13

$$f_z = \frac{1}{2\pi \cdot C_{out} \cdot R_{TOT}}$$

and:

**Equation 14**

$$R_{TOT} = ESR + R_{VESR}$$

Moreover, the  $C_{INT}$  capacitor must meet the following condition:

**Equation 15**

$$f_{SW} > k \cdot f_Z = \frac{k}{2\pi \cdot C_{out} \cdot R_{TOT}}$$

where  $R_{TOT}$  is the sum of the ESR of the output capacitor and the equivalent ESR given by the Virtual-ESR Network ( $R_{VESR}$ ). The  $k$  parameter must be greater than unity ( $k > 3$ ) and determines the minimum integrator capacitor value  $C_{INT}$ :

**Equation 16**

$$C_{INT} > \frac{g_m}{2\pi \cdot \left( \frac{f_{SW}}{k} - f_Z \right)} \cdot \frac{V_r}{V_{out}}$$

The capacitor of the virtual-ESR Network,  $C$ , is chosen as follows:

**Equation 17**

$$C > 5 \cdot C_{INT}$$

and  $R$  is calculated to provide the desired triangular ripple voltage:

**Equation 18**

$$R = \frac{L}{R_{VESR} \cdot C}$$

Finally the  $R_1$  resistor is calculated according to expression 19:

**Equation 19**

$$R_1 = \frac{R \cdot \left( \frac{1}{C \cdot \pi \cdot f_Z} \right)}{R - \frac{1}{C \cdot \pi \cdot f_Z}}$$

### 7.1.3 Pulse-skip and no-audible pulse-skip modes

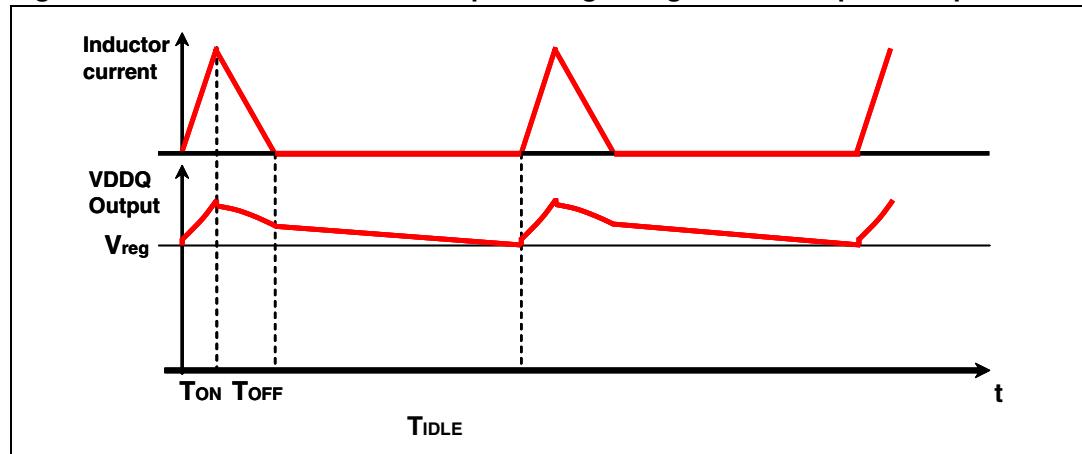

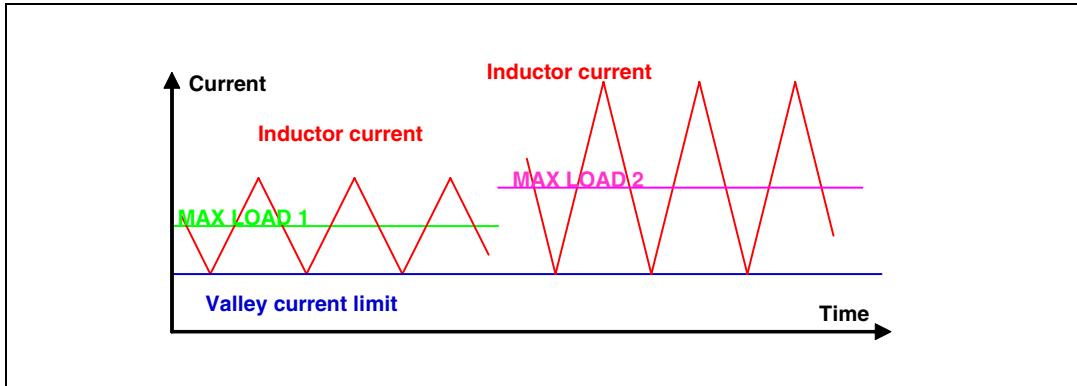

High efficiency at light load conditions is achieved by PM6670S entering the pulse-skip mode (if enabled). When one of the two fixed output voltages is set, pulse-skip power saving is a default feature. At light load conditions the zero-crossing comparator truncates the low-side switch on-time as soon as the inductor current becomes negative; in this way the comparator determines the on-time duration instead of the output ripple (see [Figure 33](#)).

**Figure 33. Inductor current and output voltage at light load with pulse-skip**

As a consequence, the output capacitor is left floating and its discharge depends solely on the current drained from the load. When the output ripple on the pin COMP falls under the reference, a new shot is triggered and the next cycle begins. The pulse-skip mode is naturally obtained enabling the zero-crossing comparator and automatically takes part in the COT algorithm when the inductor current is about half the ripple current amount, i.e. migrating from continuous conduction mode (C.C.M.) to discontinuous conduction mode (D.C.M.).

The output current threshold related to the transition between PWM mode and pulse-skip mode can be approximately calculated as:

**Equation 20**

$$I_{LOAD}(\text{PWM2Skip}) = \frac{V_{IN} - V_{OUT}}{2 \cdot L} \cdot T_{ON}$$

At higher loads, the inductor current never crosses zero and the device works in pure PWM mode with a switching frequency around the nominal value.

A physiological consequence of pulse-skip mode is a more noisy and asynchronous (than normal conditions) output, mainly due to very low load. If the pulse-skip is not compatible with the application, the PM6670S, when set in adjustable mode-of-operation, allows the user to choose between forced-PWM and no-audible pulse-skip alternative modes (see [Chapter 7.1.4 on page 30](#) for details).

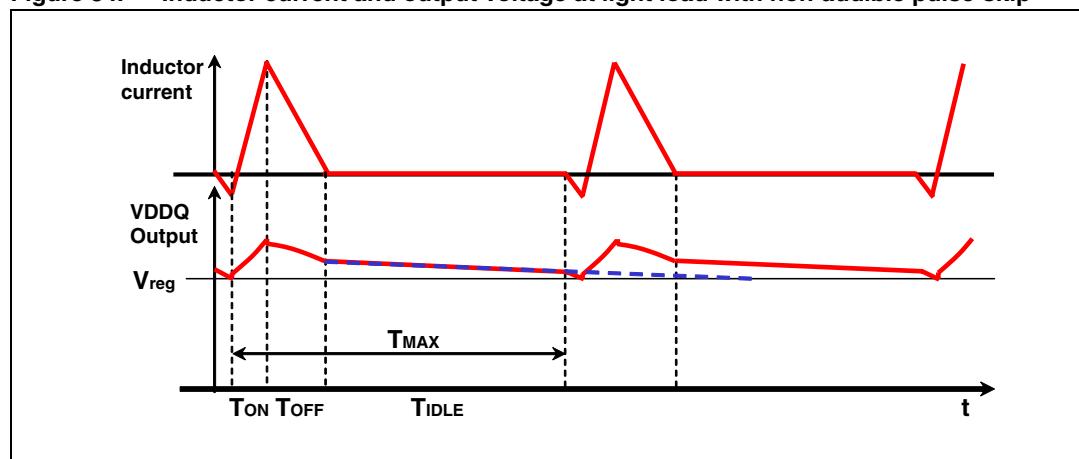

### No-audible pulse-skip mode

Some audio-noise sensitive applications cannot accept the switching frequency to enter the audible range as is possible in pulse-skip mode with very light loads. For this reason, the PM6670S implements an additional feature to maintain a minimum switching frequency of 33 kHz despite a slight efficiency loss. At very light load conditions, if any switching cycle has taken place within 30  $\mu$ s (typ.) since the last one (because the output voltage is still higher than the reference), a no-audible pulse-skip cycle begins. The low-side MOSFET is turned on and the output is driven to fall until the reference has been crossed. Then, the high-side switch is turned on for a  $T_{ON}$  period and, once it has expired, the synchronous rectifier is enabled until the inductor current reaches the zero-crossing threshold (see [Figure 34](#)).

**Figure 34.** Inductor current and output voltage at light load with non-audible pulse-skip

For frequencies higher than 33 kHz (due to heavier loads) the device works in the same way as in pulse-skip mode. It is important to notice that in both pulse-skip and no-audible pulse-skip modes the switching frequency changes not only with the load but also with the input voltage.

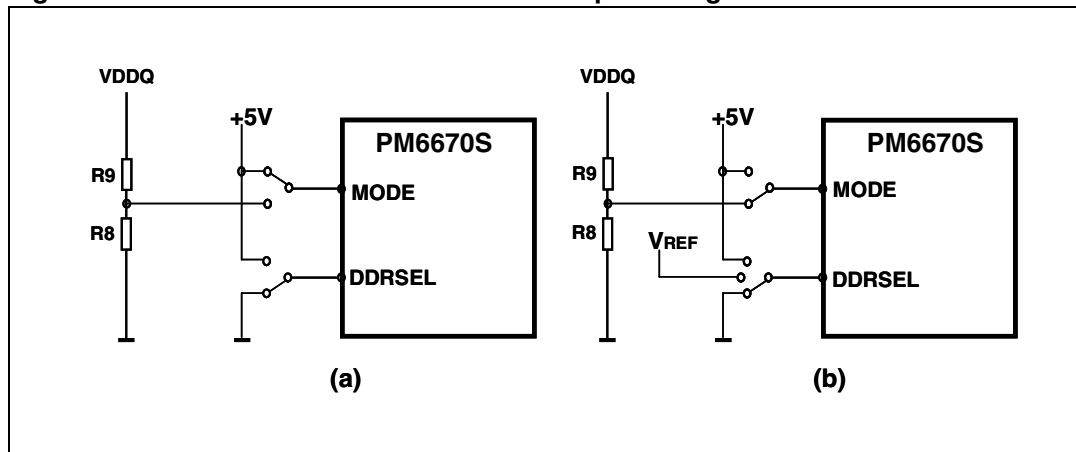

### 7.1.4 Mode-of-operation selection

Figure 35. MODE and DDRSEL multifunction pin configurations

The PM6670S has been designed to satisfy the widest range of applications involving DDR2/3 memories, SSTL15-18 buses termination and I/O supplies for CPU/chipset. The device is provided with multilevel pins which allow the user to choose the appropriate configuration. The MODE pin is used to firstly decide between fixed preset or adjustable (user defined) output voltages.

When the MODE pin is connected to +5 V, the PM6670S allows setting the VDDQ voltage to 1.8 V or 1.5 V just forcing the DDRSEL multilevel pin to +5 V or to ground respectively (see [Figure 35a](#)).

In this condition the pulse-skip feature is enabled. This device configuration is suitable for standard DDR2/3 memory supply applications avoiding the need for an external, high accuracy, divider for output voltage setting.

Applications requiring different output voltages can be managed by PM6670S simply setting the adjustable mode. If MODE pin voltage is higher than 4 V, the fixed output mode is selected. Connecting an external divider to the MODE pin ([Figure 35b](#)), it is used as negative input of the error amplifier and the output voltage is given by expression (21).

#### Equation 21

$$VDDQ_{ADJ} = 0.9 \cdot \frac{R8 + R9}{R8}$$

VDDQ output voltage can be set in the range of 0.9 V to 2.6 V. Adjustable mode automatically switches DDRSEL pin to become the power saving algorithm selector: if tied to +5 V, the forced-PWM (fixed frequency) control is performed. If grounded or connected to VREF pin (1.237 V reference voltage), the pulse-skip or non-audible pulse-skip modes are respectively selected.

**Table 8. Mode-of-operation settings summary**

| Mode                      | DDRSEL                                  | VDDQ  | Operating mode         |  |

|---------------------------|-----------------------------------------|-------|------------------------|--|

| $V_{MODE} > 4.3\text{ V}$ | $V_{DDRSEL} > 4.2\text{ V}$             | 1.8 V | Pulse-skip             |  |

|                           | $1\text{V} < V_{DDRSEL} < 3.5\text{ V}$ | 1.5 V |                        |  |

|                           | $< 0.5\text{ V}$                        |       |                        |  |

| $V_{MODE} < 3.7\text{ V}$ | $V_{DDRSEL} > 4.2\text{ V}$             | ADJ   | Forced-PWM             |  |

|                           | $1\text{V} < V_{DDRSEL} < 3.5\text{ V}$ |       | Non-audible pulse-skip |  |

|                           | $V_{DDRSEL} < 0.5\text{ V}$             |       | Pulse-skip             |  |

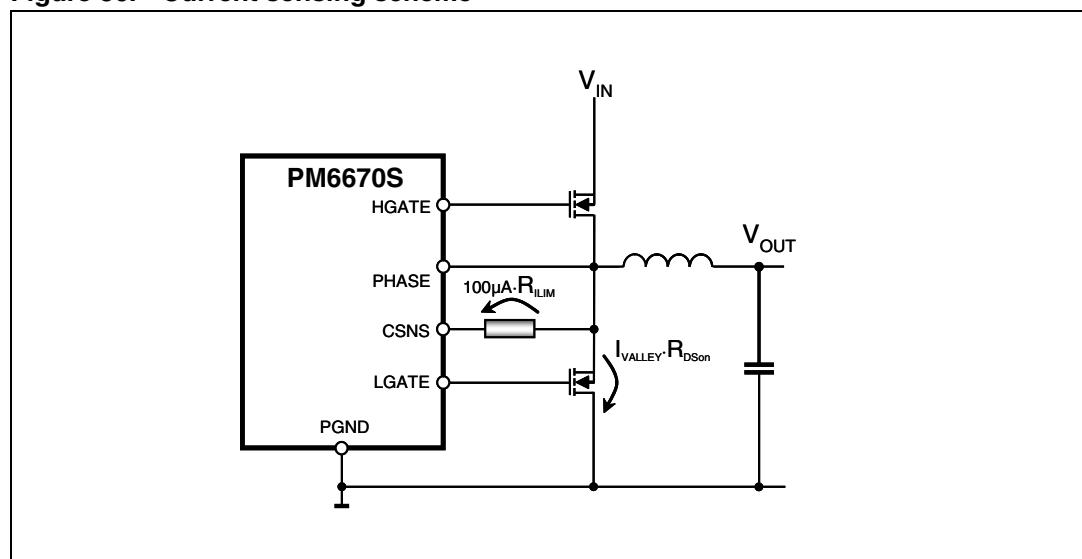

### 7.1.5 Current sensing and current limit

The PM6670S switching controller uses a valley current sensing algorithm to properly handle the current limit protection and the inductor current zero-crossing information. The current is sensed during the conduction time of the low-side MOSFET. The current sensing element is the on-resistance of the low-side switch. The sensing scheme is visible in [Figure 36](#).

**Figure 36. Current sensing scheme**

An internal 120  $\mu\text{A}$  current source is connected to CSNS pin that is also the non-inverting input of the positive current limit comparator. When the voltage drop developed across the sensing parameter equals the voltage drop across the programming resistor  $R_{ILIM}$ , the controller skips subsequent cycles until the overcurrent condition is detected or the output UV protection latches off the device (see [Section 7.1.11: Over voltage and under voltage protections on page 36](#)).

Referring to [Figure 36](#), the  $R_{DS(on)}$  sensing technique allows high efficiency performance without the need for an external sensing resistor. The on-resistance of the MOSFET is affected by temperature drift and nominal value spread of the parameter itself; this must be considered during the  $R_{ILIM}$  setting resistor design.

It must be taken into account that the current limit circuit actually regulates the inductor valley current. This means that  $R_{ILIM}$  must be calculated to set a limit threshold given by the maximum DC output current plus half of the inductor ripple current:

#### Equation 22

$$I_{CL} = 120\mu A \cdot \frac{R_{ILIM}}{R_{DSon}}$$

The PM6670S provides also a fixed negative current limit to prevent excessive reverse inductor current when the switching section sinks current from the load in forced-PWM (3<sup>rd</sup> quadrant working conditions). This negative current limit threshold is measured between PHASE and PGND pins, comparing the drop magnitude on PHASE pin with an internal 110 mV fixed threshold.

#### 7.1.6 POR, UVLO and soft-start

The PM6670S automatically performs an internal startup sequence during the rising phase of the analog supply of the device (AVCC). The switching controller remains in a stand-by state until AVCC crosses the upper UVLO threshold (4.25 V typ.), keeping active the internal discharge MOSFETs (only if AVCC > 1 V).

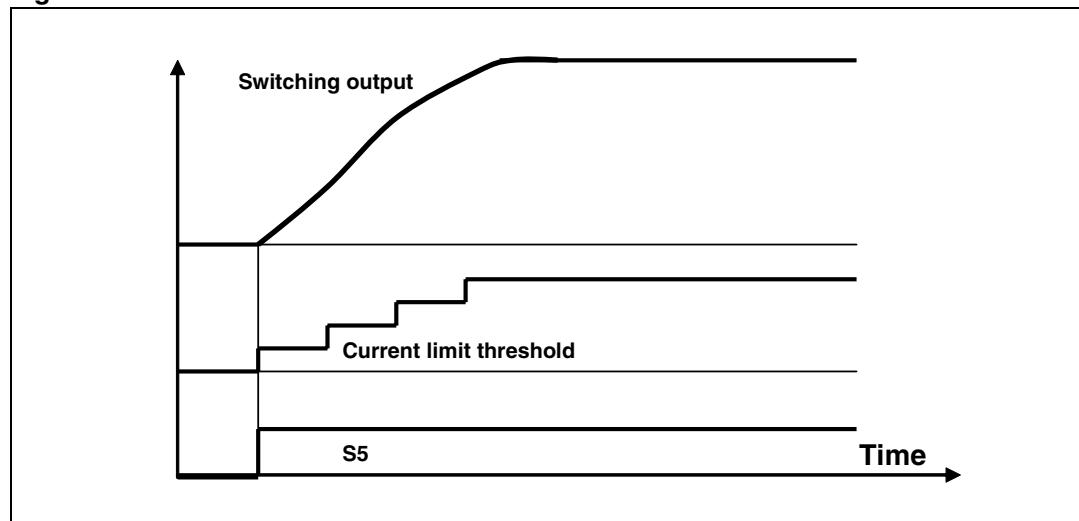

The soft-start allows a gradual increase of the internal current limit threshold during start-up reducing the input/output surge currents. At the beginning of start-up, the PM6670S current limit is set to 25 % of nominal value and the under voltage protection is disabled. Then, the current limit threshold is sequentially brought to 100 % in four steps of approximately 750  $\mu$ s ([Figure 37](#)).

**Figure 37. Soft-start waveforms**

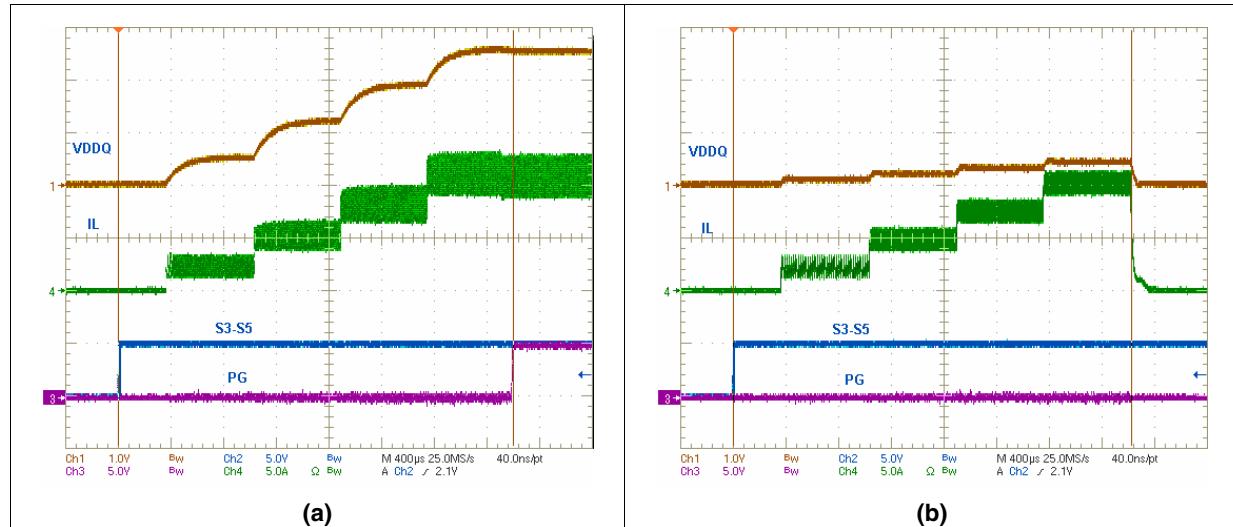

After a fixed 3 ms total time, the soft-start finishes and UVP is released: if the output voltage doesn't reach the under voltage threshold within soft-start duration, the UVP condition is detected and the device performs a soft end and latches off. Depending on the load conditions, the inductor current may or may not reach the nominal value of the current limit during the soft-start ([Figure 38](#) shows two examples).

**Figure 38. Soft-start at heavy load (a) and short-circuit (b) conditions, pulse-skip enabled**

### 7.1.7 Power Good signal

The PG pin is an open drain output used to monitor output voltage through VSNS (in fixed output voltage mode) or MODE (in adjustable output voltage mode) pins and is enabled after the soft-start timer has expired. PG signal is held low if the VDDQ output voltage drops 10 % below or rises 10 % above the nominal regulated value. The PG output can sink current up to 4 mA.

### 7.1.8 VDDQ output discharge

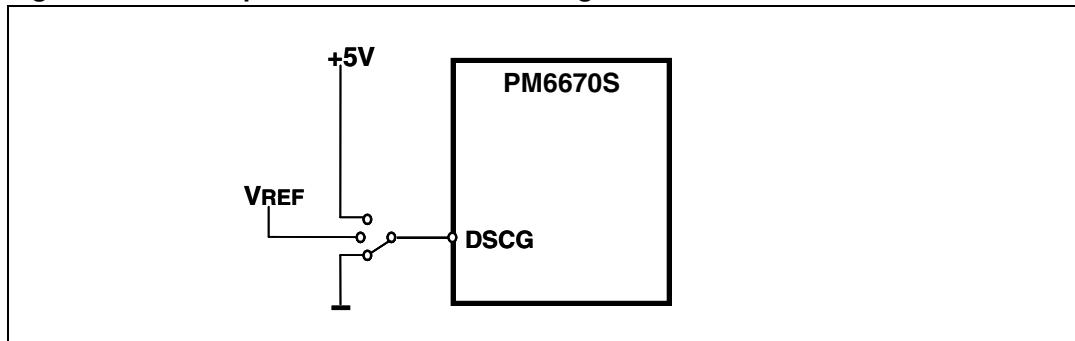

Active discharge of VDDQ output occurs when PM6670S enters the suspend-to-disk system state (S3 and S5 tied to GND) and DSCG pin has been properly set.

**Figure 39. DSCG pin connection for discharge mode selection**

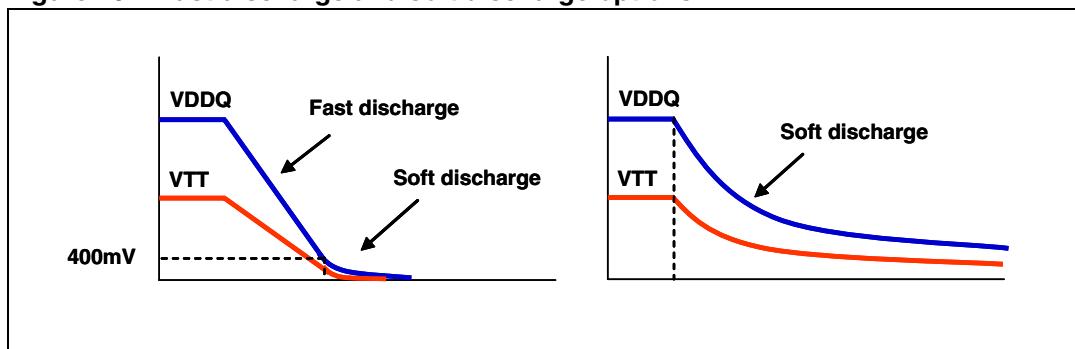

The PM6670S allows the user to choose between fast discharge (tracking discharge), soft discharge (non-tracking discharge) or no discharge modes. Voltage on DSCG multilevel pin determines discharge mode as shown in [Table 9 on page 34](#).

**Table 9. Discharge mode selection**

| DSCG voltage        | Soft-End type       | Description                                                         |

|---------------------|---------------------|---------------------------------------------------------------------|

| VDSCG > 4.2 V       | No discharge        | All outputs left floating.                                          |

| 1 V < VDSCG < 3.5 V | Fast (tracking)     | VDDQ and VTT actively discharged by LDO through LDOIN and VTT pins; |

| VDSCG < 0.5 V       | Soft (non-tracking) | All outputs discharged by dedicated internal MOS.                   |

Tracking discharge allows the fastest discharge of all outputs but requires the LDOIN to be self-supplied from VDDQ output voltage. When an external supply rail is connected to LDOIN, it must be taken into account to avoid damage to the device. Discharge current (1 A) flows through the LDOIN pin until the output has reached approximately 400 mV and then a soft discharge completes the process by discharging the output with an internal 22  $\Omega$  switch.

**Figure 40. Fast discharge and soft discharge options**

### 7.1.9 Gate drivers

The integrated high-current gate drivers allow using different power MOSFETs. The high-side driver uses a bootstrap circuit which is supplied by the +5 V rail. The BOOT and PHASE pins work respectively as supply and return path for the high-side driver, while the low-side driver is directly fed through VCC and PGND pins.

An important feature of the PM6670S gate drivers is the adaptive anti-cross-conduction circuitry, which prevents high-side and low-side MOSFETs from being turned on at the same time. When the high-side MOSFET is turned off, the voltage at the PHASE node begins to fall. The low-side MOSFET is turned on only when the voltage at the PHASE node reaches an internal threshold (2.5 V typ.). Similarly, when the low-side MOSFET is turned off, the high-side one remains off until the LGATE pin voltage is above 1V.

The power dissipation of the drivers is a function of the total gate charge of the external power MOSFETs and the switching frequency, as shown in the following equation:

#### Equation 23

$$P_D(\text{driver}) = V_{\text{DRV}} \cdot Q_g \cdot f_{\text{SW}}$$

The low-side driver has been designed to have a low-resistance pull-down transistor (0.6  $\Omega$  typ.) in order to prevent undesired ignition of the low-side MOSFET due to the Miller effect.

### 7.1.10 Reference voltage and bandgap

The 1.237 V internal bandgap reference has a granted accuracy of  $\pm 1\%$  over the 0  $^{\circ}\text{C}$  to 85  $^{\circ}\text{C}$  temperature range. The VREF pin is a buffered replica of the bandgap voltage. It can supply up to  $\pm 100 \mu\text{A}$  and is suitable to set the intermediate level of MODE, DDRSEL and DSCG multifunction pins. A 100 nF (min.) bypass capacitor toward SGND is required to enhance noise rejection. If VREF falls below 0.8 V (typ.), the system detects a fault condition and all the circuitry is turned OFF.

An internal divider derives a 0.9 V  $\pm 1\%$  voltage (V<sub>r</sub>) from the bandgap. This voltage is used as a reference by the switching regulator output. The over-voltage protection, the under-voltage protection and the power good signal are also referred to V<sub>r</sub>.

### 7.1.11 Over voltage and under voltage protections

When the switching output voltage is about 115 % of its nominal value, a latched over-voltage protection (OVP) occurs. In this case the synchronous rectifier immediately turns on while the high-side MOSFET turns OFF. The output capacitor is rapidly discharged and the load is preserved from being damaged. The OVP is also active during the soft start. Once an OVP has occurred, a toggle on S5 pin or a power-on-reset is necessary to exit from the latched state.

When the switching output voltage is below 70 % of its nominal value, a latched under-voltage protection occurs. This event causes the switching section to be immediately disabled and both switches to be opened. The controller enters in soft-end mode and the output is eventually kept to ground, turning the low side MOSFET on when the voltage is lower than 400 mV. If S3 and S5 are forced low, the low-side MOSFET is released and only the  $22\ \Omega$  switch is active.

The under-voltage protection circuit is enabled only at the end of the soft-start. Once an UVP has occurred, a toggle on S5 pin or a power-on-reset is necessary to clear the fault state and restart the device.

### 7.1.12 Device thermal protection

The internal control circuitry of the PM6670S self-monitors the junction temperature and turns all outputs off when the  $150\ ^\circ\text{C}$  limit has been overrun. This event causes the switching section to be immediately disabled and both switches to be opened. The controller enters in Soft-End Mode and the output is eventually kept to ground, turning the low side MOSFET on when the voltage is lower than 400 mV. If S3 and S5 are forced low, the low-side switch is released and only the  $22\ \Omega$  discharge MOSFET is active.

The thermal fault is a latched protection and normal operating condition is restored by a Power-on reset or toggling S5.

**Table 10. OV, UV and OT faults management**

| Fault                     | Conditions                                          | Action                                                                                                                                                         |

|---------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDDQ over voltage         | $\text{VDDQ} > 115\ \%\text{ of the nominal value}$ | LGATE pin is forced high and the device latches off. Exit by a power-on reset or toggling S5                                                                   |

| VDDQ under voltage        | $\text{VDDQ} < 70\ \%\text{ of the nominal value}$  | LGATE pin is forced high after the soft-end, then the device latches off. Exit by a power-on reset or toggling S5.                                             |

| Junction over temperature | $T_J > +150\ ^\circ\text{C}$                        | LGATE pin is forced high after the soft-end, then the device latches off. Exit by a power-on reset or toggling S5 after $15\ ^\circ\text{C}$ temperature drop. |

## 7.2 VTTREF buffered reference and VTT LDO section

The PM6670S provides the required DDR2/3 reference voltage on the VTTREF pin. The internal buffer tracks half the voltage on the VSNS pin and has a sink and source capability up to 15 mA.

Higher currents rapidly deteriorate the output accuracy. A 10 nF to 100 nF (33 nF typ.) bypass capacitor to SGND is required for stability.

The VTT low-drop-out linear regulator has been designed to sink and source up to 2 A peak current and 1 A continuously. The VTT voltage tracks VTTREF within  $\pm 35$  mV.

A remote voltage sensing pin (VTTSNS) is provided to recovery voltage drops due to parasitic resistance. In DDR2/3 applications, the linear regulator input LDOIN is typically connected to VDDQ output; connecting LDOIN pin to a lower voltage, if available in the system, reduces the power dissipation of the LDO.

A minimum output capacitance of 20  $\mu$ F (2x10  $\mu$ F MLCC capacitors) is enough to assure stability and fast load transient response.

### 7.2.1 VTT and VTTREF Soft-Start

Soft-Start on VTT and VTTREF outputs is achieved by current clamping.

The LDO linear regulator is provided with a current foldback protection: when the output voltage exits the internal  $\pm 10$  % VTT-Good window, the output current is clamped at  $\pm 1$  A. Re-entering VTT-Good window releases the current limit clamping.

The foldback mechanism naturally implements a two steps soft-start charging the output capacitors with a 1 A constant current.

Something similar occurs at VTTREF pin, where the output capacitor is smoothly charged at a fixed 40 mA current limit.

### 7.2.2 VTTREF and VTT outputs discharge

The tracking discharge mechanism involves the VTT linear regulator. When the suspend-to-disk state is entered, the switching regulator is turned OFF.

At the same time the LDO drains a 1 A constant current from LDOIN and keeps VTT in track with VTTREF that, in turn, is half the voltage at the VSNS pin. When the VDDQ output reaches 400 mV, the PM6670S switches on the internal discharge MOSFETs to complete the process (see [Section 7.1.8: VDDQ output discharge on page 34](#)).

In soft discharge (i.e. non-tracking discharge) the PM6670S disables the internal regulators and suddenly turns on the discharge MOSFETs on each output.

## 7.3 S3 and S5 power management pins

According to DDR2/3 memories supply requirements, the PM6670S can manage all S0 to S5 system states by connecting S3-S5 pins to their respective sleep-mode signals in the notebook motherboard.

Keeping S3 and S5 high, the S0 (Full-On) state is decoded and the outputs are alive.

In S3 state (S5 = 1, S3 = 0), the PM6670S maintains VDDQ and VTTREF outputs active and VTT output in high-impedance as needed.

In S4/S5 states (S5 = S3 = 0) all outputs are turned off and, according to DSCG pin voltage, the proper Soft-End is performed.

**Table 11. S3 and S5 sleep-states decoding**

| S3 | S5 | System state            | VDDQ            | VTTREF          | VTT             |

|----|----|-------------------------|-----------------|-----------------|-----------------|

| 1  | 1  | S0 (full-On)            | On              | On              | On              |

| 0  | 1  | S3 (suspend-to-RAM)     | On              | On              | Off (Hi-Z)      |

| 0  | 0  | S4/S5 (suspend-to-Disk) | Off (discharge) | Off (discharge) | Off (discharge) |

## 8 Application information

The purpose of this chapter is to show the design procedure of the switching section.

The design starts from three main specifications:

- The input voltage range, provided by the battery or the AC adapter. The two extreme values ( $V_{INMAX}$  and  $V_{INmin}$ ) are important for the design.

- The maximum load current, indicated by  $I_{LOAD,MAX}$ .

- The maximum allowed output voltage ripple  $V_{RIPPLE,MAX}$ .

It's also possible that specific designs should involve other specifications.

The following paragraphs will guide the user into a step-by-step design.

### 8.1 External components selection

The PM6670S uses a pseudo-fixed frequency, constant on-time (COT) controller as the core of the switching section. The switching frequency can be set by connecting an external divider to the VOSC pin. The voltage seen at this pin must be greater than 0.8 V and lower than 2 V in order to ensure system's linearity.

Nearly constant switching frequency is achieved by the system's loop in steady-state operating conditions by varying the on-time duration, avoiding thus the need for a clock generator. The On-Time one shot duration is directly proportional to the output voltage, sensed at VSNS pin, and inversely proportional to the input voltage, sensed at the VOSC pin, as follows:

#### Equation 24

$$T_{ON} = K_{OSC} \frac{V_{SNS}}{V_{OSC}} + \tau$$

where  $K_{OSC}$  is a constant value (130 ns typ.) and  $\tau$  is the internal propagation delay (40 ns typ.).

The duty cycle of the buck converter is, under steady state conditions, given by

#### Equation 25

$$D = \frac{V_{OUT}}{V_{IN}}$$

The switching frequency is thus calculated as

#### Equation 26

$$f_{SW} = \frac{D}{T_{ON}} = \frac{\frac{V_{OUT}}{V_{IN}}}{K_{OSC} \cdot \frac{V_{SNS}}{V_{OSC}}} = \frac{\alpha_{OSC}}{\alpha_{OUT}} \cdot \frac{1}{K_{OSC}}$$

where

**Equation 27a**

$$\alpha_{\text{OSC}} = \frac{V_{\text{OSC}}}{V_{\text{IN}}}$$

**Equation 27b**

$$\alpha_{\text{OUT}} = \frac{V_{\text{SNS}}}{V_{\text{OUT}}}$$

Referring to the typical application schematic (figure in cover page and [Figure 29](#)), the final expression is then:

**Equation 28**

$$f_{\text{SW}} = \frac{\alpha_{\text{OSC}}}{K_{\text{OSC}}} = \frac{R_2}{R_1 + R_2} \cdot \frac{1}{K_{\text{OSC}}}$$

The switching frequency directly affects two parameters:

- Inductor size: greater frequencies mean smaller inductances. In notebook applications, real estate solutions (i.e. low-profile power inductors) are mandatory also with high saturation and r.m.s. currents.

- Efficiency: switching losses are proportional to the frequency. Generally, higher frequencies imply lower efficiency.

Even if the switching frequency is theoretically independent from battery and output voltages, parasitic parameters involved in power path (like MOSFETs on-resistance and inductor DCR) introduce voltage drops responsible for a slight dependence on load current.

In addition, the internal delay is due to a light dependence on input voltage.

**Table 12. Typical values for switching frequency selection**

| R1 (kΩ) | R2 (kΩ) | Approx switching frequency (kHz) |

|---------|---------|----------------------------------|

| 330     | 11      | 250                              |

| 330     | 13      | 300                              |

| 330     | 15      | 350                              |

| 330     | 18      | 400                              |

| 330     | 20      | 450                              |

| 330     | 22      | 500                              |

### 8.1.1 Inductor selection

Once the switching frequency has been defined, the inductance value depends on the desired inductor ripple current. Low inductance value means great ripple current that brings poor efficiency and great output noise. On the other hand a great current ripple is desirable for fast transient response when a load step is applied.

High inductance brings higher efficiency, but the transient response is critical, especially if  $V_{IN,MIN} - V_{OUT}$  is small. Moreover a minimum output ripple voltage is necessary to assure system stability and jitter-free operations (see output capacitor selection paragraph). The product of the output capacitor's ESR multiplied by the inductor ripple current must be taken into consideration. A good trade-off between the transient response time, the efficiency, the cost and the size is choosing the inductance value in order to maintain the inductor ripple current between 20 % and 50 % (usually 40 %) of the maximum output current.

The maximum inductor ripple current,  $\Delta I_{L,MAX}$ , occurs at the maximum input voltage.

Given these considerations, the inductance value can be calculated with the following expression:

#### Equation 29

$$L = \frac{V_{IN} - V_{OUT}}{f_{SW} \cdot \Delta I_L} \cdot \frac{V_{OUT}}{V_{IN}}$$

where  $f_{SW}$  is the switching frequency,  $V_{IN}$  is the input voltage,  $V_{OUT}$  is the output voltage and  $\Delta I_L$  is the inductor ripple current.

Once the inductor value is determined, the inductor ripple current is then recalculated:

#### Equation 30

$$\Delta I_{L,MAX} = \frac{V_{IN,MAX} - V_{OUT}}{f_{SW} \cdot L} \cdot \frac{V_{OUT}}{V_{IN,MAX}}$$

The next step is the calculation of the maximum r.m.s. inductor current:

#### Equation 31

$$I_{L,RMS} = \sqrt{(I_{LOAD,MAX})^2 + \frac{(\Delta I_{L,MAX})^2}{12}}$$

The inductor must have an r.m.s. current greater than  $I_{L,RMS}$  in order to assure thermal stability.

Then the calculation of the maximum inductor peak current follows:

#### Equation 32

$$I_{L,PEAK} = I_{LOAD,MAX} + \frac{\Delta I_{L,MAX}}{2}$$

$I_{L,PEAK}$  is important in inductor selection in term of its saturation current.

The saturation current of the inductor should be greater than  $I_{L,PEAK}$  not only in case of hard saturation core inductors. Using soft-ferrite cores it is possible (but not advisable) to push the inductor working near its saturation current.